#### UNIVERSITY OF PENNSYLVANIA

MOORE SCHOOL

THE DESIGN OF THE

PARALLEL ARITHMETIC UNIT

IN PEPE

#### MARK CAMILLO DIVECCHIO

Presented to the Faculty of the College of Engineering and Applied Science (Department of Computer and Information Sciences) in partial fulfillment of the requirements for the degree of Master of Science in Engineering.

Philadelphia, Pennsylvania August 1978

Dr. John W. Carr III

Dr. A. K. Joshi

nsnas

UNIVERSITY

OF

PENNSYLVANIA

LIBRARIES

# 1.0 The Parallel Element Processing Ensemble (PEPE)

#### 1.1 Overview

As the need for solutions to high speed processing problems increases, new and novel architectures will be developed. PEPE is an attempt to solve a specific real-time problem with use of special purpose hardware.

The Ballistic Missile Defense Advanced Technology Center in Huntsville, Alabama started development studies in the late 1960s for a processor to offload the ever increasing demands on a serial processor operating in a ballistic missile defense (BMD) environment.

PEPE's design specifically addresses the BMD problem. It was designed to perform three basic functions previously allocated to a CDC 7700 system. They are:

- · Correlation of new radar returns with current tracks

- · Track prediction on all current tracks

- Scheduling on a radar time/power line, pulses to acquire more data on current or new tracks.

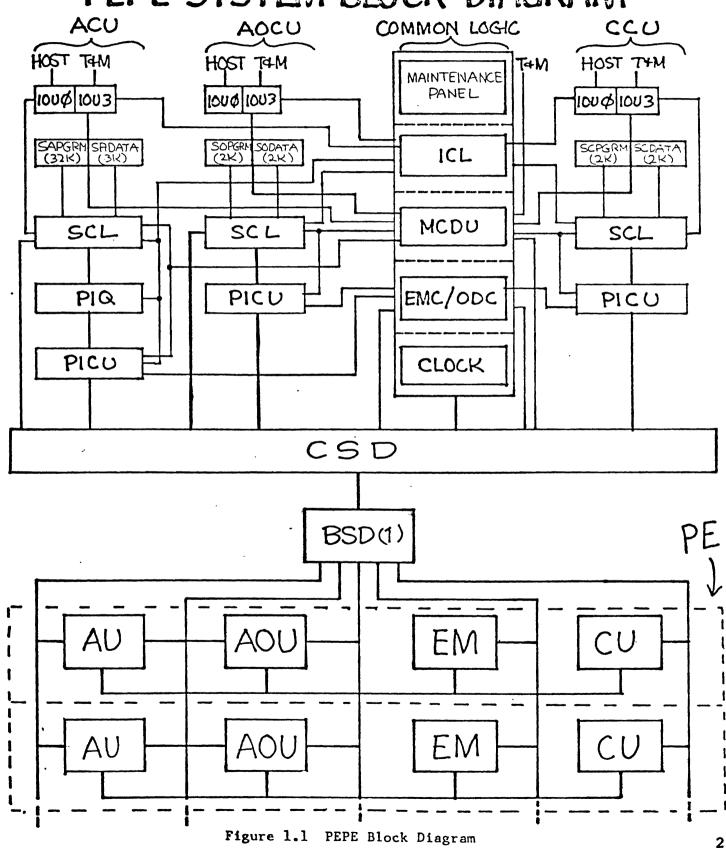

To solve these three problems, a unique multiprocessor parallel ensemble was proposed. Shown in Figure 1.1, PEPE consists of three independent control processors each commanding an ensemble of up to 288 Processing Elements (PE). The three control processors, housed in a single cabinet called a Control Console (CC), are identical with minor exceptions. Each contains:

- Sequential Control Logic (SCL)

- · Program and Data Memories

- I/O Units

- Parallel Instruction Control Unit (PICU)

# PEPE SYSTEM BLOCK DIAGRAM

The SCL is a stand alone processor with all facilities for program execution from memory. It performs typical arithmetic, logical, comparison, and branching functions of a sequential machine. The I/O units perform high speed input and output to the CDC 7700 using a direct channel to both program and data memories.

The PICU receives parallel instructions from the SCL. As the SCL fetches an instruction from memory, it determines if that instruction is targeted for execution in the SCL or in the parallel ensemble. Instructions for the ensemble are sent to the PICU. Described more fully in Section 4.2, the PICU decodes each parallel instruction and transmits control information to all 288 PE.

The three control units are named for their major function. The Correlation Control Unit (CCU) controls the Correlation Unit (CU) portion of the PE. Second, the Arithmetic Control Unit (ACU) handles the Arithmetic Unit (AU) and lastly, the Associative Output Control Unit (AOCU) controls the Associative Output Unit (AOU).

Other major units in the CC are the Intercommunication Logic (ICL), the Output Data Control (ODC) and the Element Memory Control (EMC). The ICL handles communication between the three SCL's and handles interrupt vectoring and masking. The ODC controls access to the main data bus used for outputting data from the ensemble. This bus is a single path shared between all AU and AOU of the ensemble. EMC controls the granting of cycles of the Element Memory (EM) which is shared between processors of the PE.

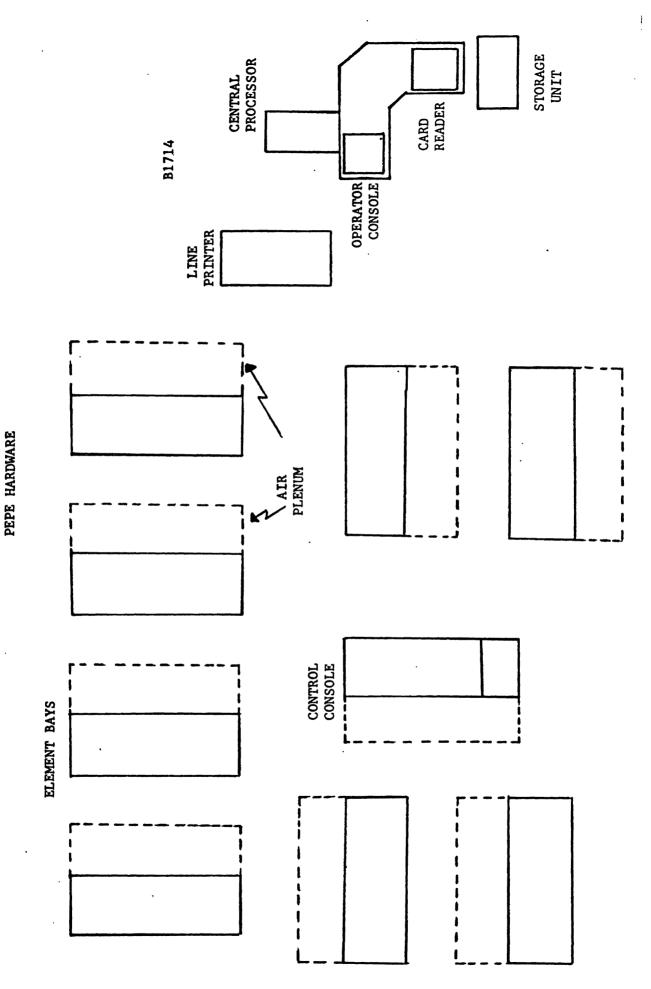

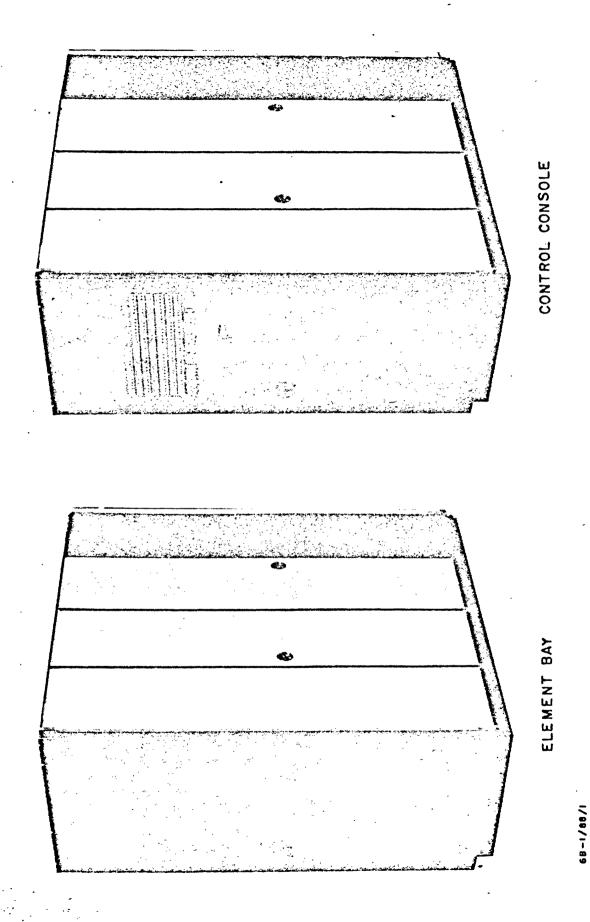

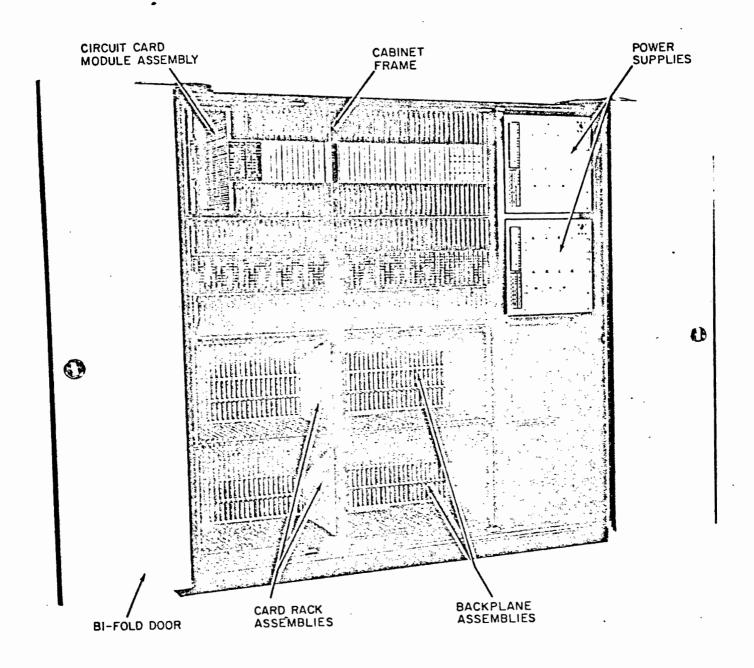

Figure 1.2 shows the floor layout of a PEPE installation. The CC is centrally located since it must communicate with each of the 8 Element Bays (EB). A Burroughs B1714 computer is the Test and Maintenance (T&M) unit for PEPE. Figure 1.3 is a picture of PEPE installed in Huntsville, Alabama.

### 1.1.1 The Element Bay

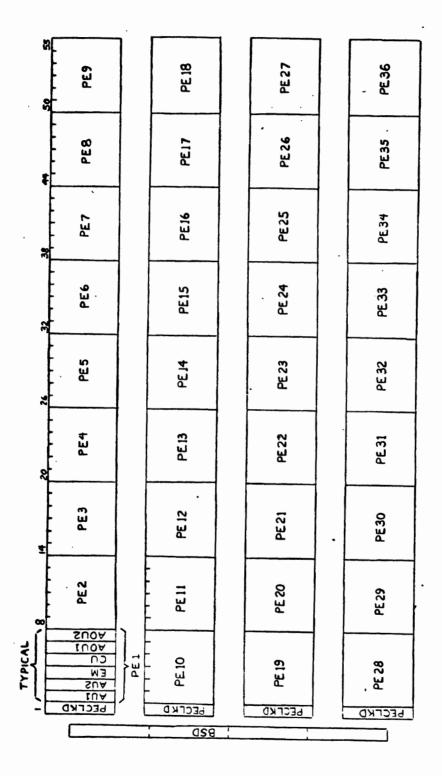

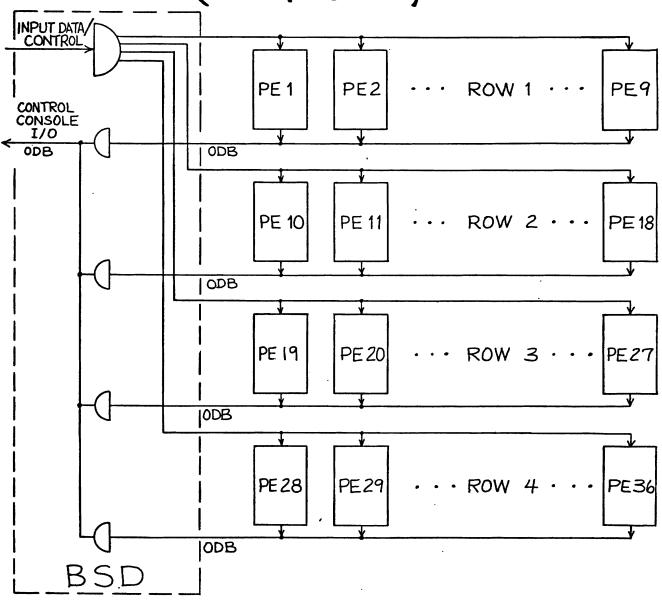

Each EB contains 36 PE as shown in Figure 1.4. The PE are laid out in 4 rows of 9 PE. Each row also contains a clock distribution card.

Figure 1.5 is a close up picture of the Element Bay with 11 PE.

One PE consists of 6 large 300 DIP boards, allocated as follows:

• AU 2 boards

• EM 1 board

• CU 1 board

• AOU 2 boards

The Bay Signal Distributor (BSD) occupies the left end of the cabinet.

The BSD provides connectors and gates to relay control and data signals from the CC to each PE and to gather output from the PE on the Output Data Bus (ODB) and relay that back to the CC. A simplified layout is shown symbolically in Figure 1.6.

5

Figure 1.4 PE Bay Layout

Figure 1.5 PE Bay with 11 PE Installed

# PE BAY-PARALLEL ORGANIZATION (SYMBOLIC)

Figure 1.6 Busing Diagram

#### 1.2 Number Formats

Crucial to the understanding of the operation of a complex floating point processor such as the AU, is a detailed knowledge of the number formats processed by the AU.

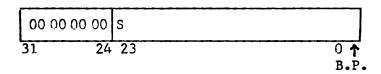

The basic PEPE word is 32 bits in length. Bits are numbered right to left with bit 31 being the most significant bit (MSB).

# 1.2.1 Integer Format

PEPE integers are stored in the lower 24 bits of a word. The upper right bits are always zero.

Bit 23 is the sign bit for the two's complement representation of the number in bits 22-0. The Range of values for integers is

$$+2^{23}-1 \geqslant integer \geqslant -2^{23}$$

A sign of "1" indicates a negative number and the binary point is considered to be to the right of bit zero.

In a two's complement number system, one more negative number may be represented than positive numbers. Consider the following for a four bit system:

BINARY DECIMAL

| BINARY  | DECIMA    |  |  |

|---------|-----------|--|--|

| 0 1 1 1 | +7        |  |  |

| 0 1 1 0 | +6        |  |  |

| •       | ;         |  |  |

| 0 0 0 0 | 0         |  |  |

| 1 1 1 1 | -1        |  |  |

| •       | •         |  |  |

| 1001    | <b>-7</b> |  |  |

| 1000    | -8        |  |  |

Plus seven is the largest positive integer and -8 is the largest negative integer. Since this -8 value does not have a positive "equivalent" we will see later that it requires special handling during the execution of certain PEPE instructions.

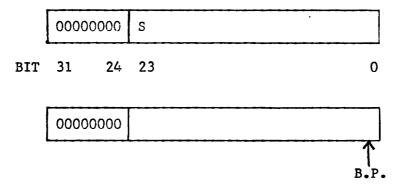

#### 1.2.2 Double Integer Format

PEPE double integers are stored in the lower 24 bits of two PEPE words. The upper 8 bits of both words are always zero. Bit 23 of the lower word is always the same as bit 0 of the upper word. Bit 23 of the upper word is the sign bit.

The range of values for double integers is

$$+2^{47}$$

-1  $\geqslant$  double integer  $\geqslant$   $-2^{47}$

The binary point (B.P.) is to right of bit 0 of the lower word. Double integers less than  $+2^{23}$ -1 or greater than  $-2^{23}$  are completely represented in the lower word as standard PEPE integers.

# 1.2.3 Logical Format

A PEPE logical word is 32 bits long with no restriction as to its contents.

#### 1.2.4 Floating Point Format

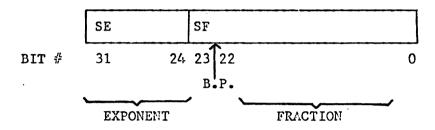

PEPE floating point numbers are represented in one 32 bit word. The fraction (or mantissa) part is stored in bits 23-0. The binary point is to the left of bit 22 and bit 23 is the sign bit of the fraction. The exponent (base 2) is stored in bits 31-24 with bit 31 being the sign bit. Both the fraction and exponent are carried in two's complement notation.

SE - Sign Exponent

SF - Sign Fraction

All floating point numbers are normalized and this is maintained by all PEPE floating point instructions. The number is considered normalized if the most significant bit of the fraction (bit 22) is different from the sign of the fraction (bit 23).

The exponent can be considered as an 8 bit integer field. Range of the exponent field is:

which can represent decimal values from (approximately):

$$10^{38} \ge \text{floating point} \ge 10^{-38}$$

and

$$-10^{-38} \geqslant$$

floating point  $\geqslant -10^{38}$ .

The range of the fraction is:

$$2^{\circ} - 2^{-23} \geqslant \text{fraction} \geqslant -2^{\circ}$$

which can represent decimal values from (approximately):

$$0.9999998^{+} \ge fraction \ge -1.0000000$$

.

The smallest magnitude fraction is .1192 X 10<sup>-6</sup>. The fraction is always less than magnitude one except for one special case of -1.0000000. This results from the same effect as discussed under integer format. PEPE floating point format allows seven significant decimal digits in the fraction.

# 1.2.4.1 Floating Point Zero

In any floating point system, a mantissa of zero with any exponent has a value of zero. Thus:

$$0.0x2^{127} = 0.0x2^{\circ} = 0.0x2^{-128}$$

PEPE hardware must, though, be able to determine equality of numbers that may both be zero. For the hardware to know that  $0.0X2^{\circ} = 0X2^{10}$ , poses difficulties that can be avoided. In PEPE, we define one floating point zero. It is:

$$0.0x2^{-128}$$

In a 32 bit word, this is a one in bit 31 and zeros in bits 30-0. All PEPE floating point instructions expect operands of zero in this form and will produce results of zero in this form. This representation can be considered the "smallest" zero in floating point format.

#### 2.0 AU Architecture at the Register Level

The Arithmetic Unit is designed to perform floating point and integer arithmetic, boolean operations, shift operations, single-bit memory data packing, overflow detection and normalize operations. Two's complement arithmetic is used. Double precision integer add and subtract instructions can be accomplished through software.

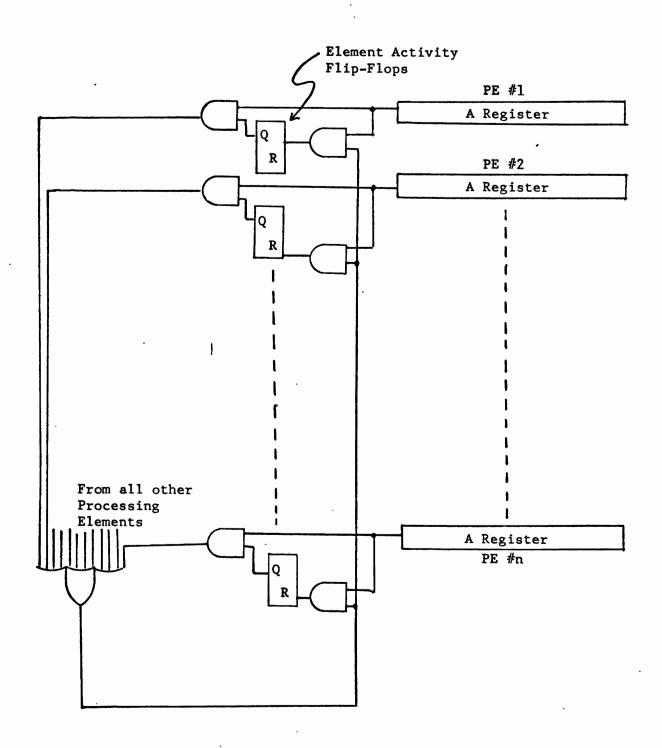

The AU also is designed to perform element activity instructions.

Activity instructions are used for selecting a set or subset of PEPE elements.

The selected set is said to be active and will have its activity flip-flop set. Elements whose activity flip-flop is not set will be inactive and will not participate in selected parallel instructions until such time as they are set active.

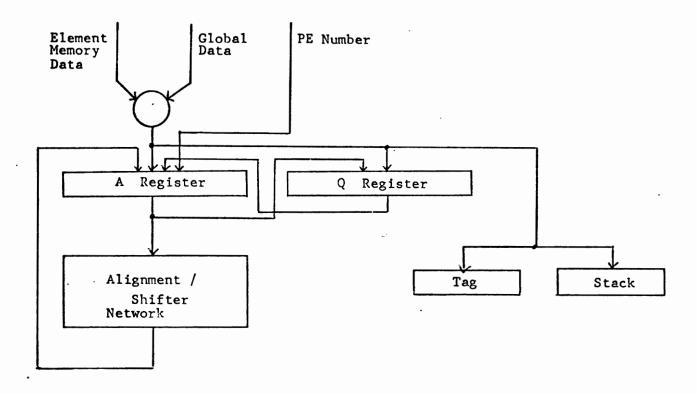

The ACU controls each AU operation through the use of control lines from the PICU. Global operands are transmitted to the AU on 32 of these lines in a time-sharing mode. In addition, element memory data transfer to and from the AU is done on 32 bidirectional lines. All data output for global use is available on 32 output data lines which are time-shared with AØU data output under global command from Output Data Control (ØDC).

Each AU also provides two outputs for the Select Highest/Lowest logic.

For observation of unit faults and as a programming aid, two overflow indicators are sent to the ICL.

The AU contains a fault flip-flop which can be set by the ACU, conditional on element activity. When this flip-flop is set it will not allow the AU, AØU, and CU of the element to participate in any instruction other than "clear fault flip-flop", which will re-enable the failed elements.

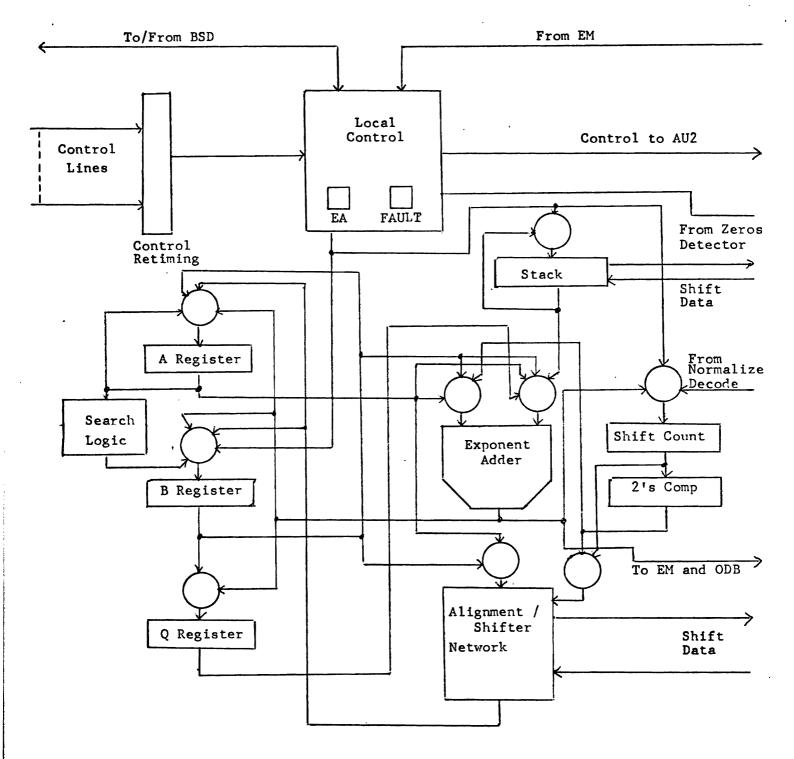

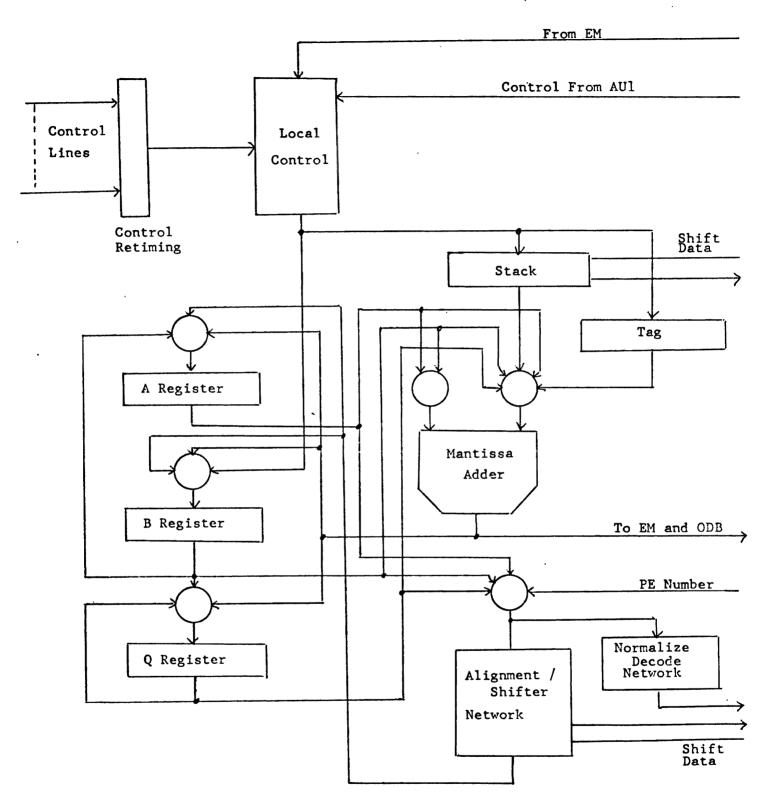

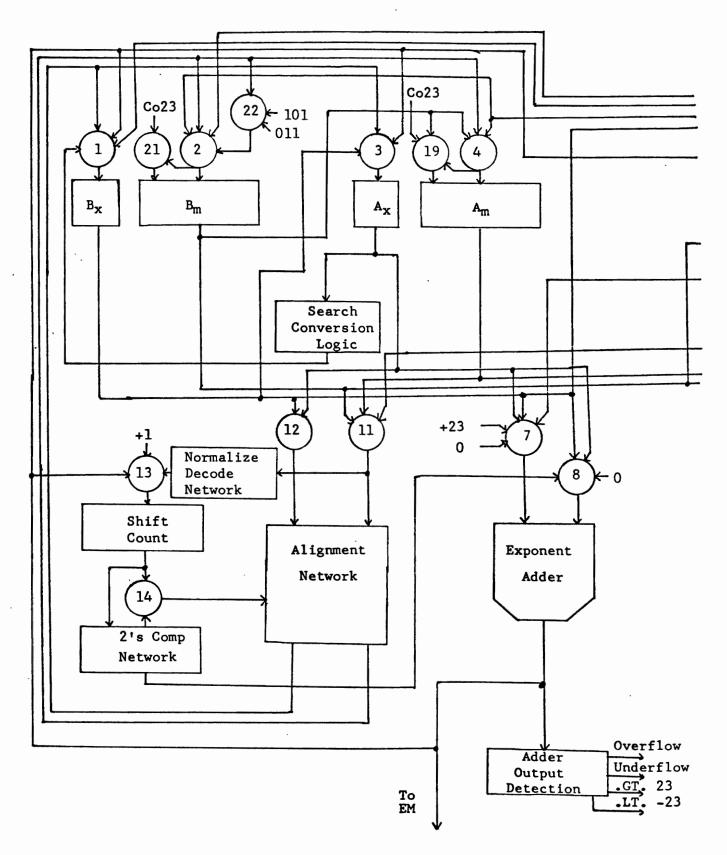

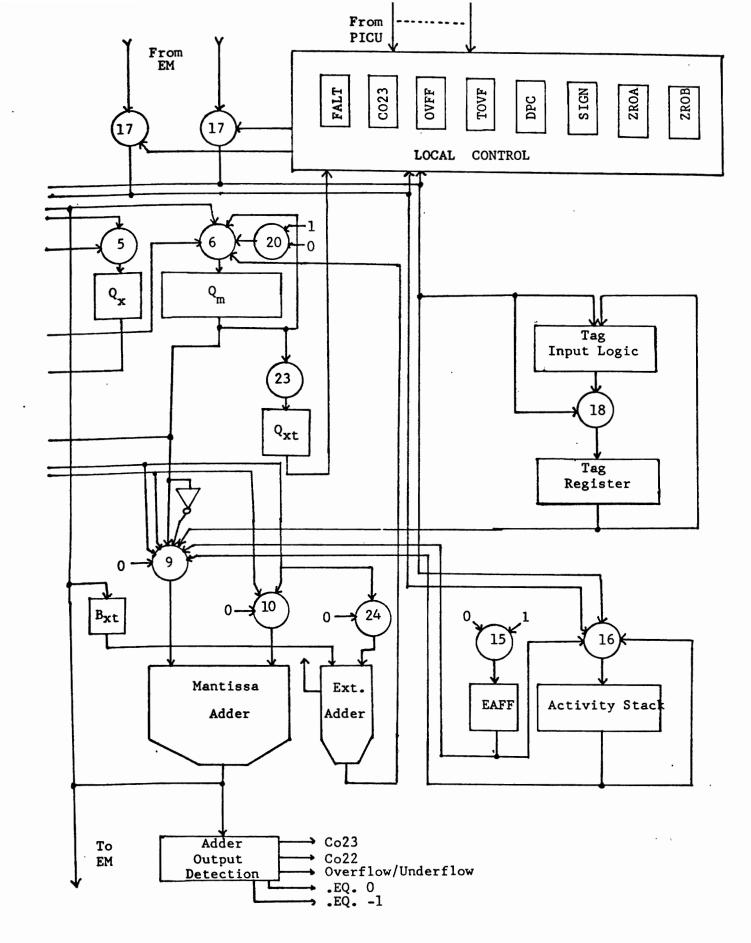

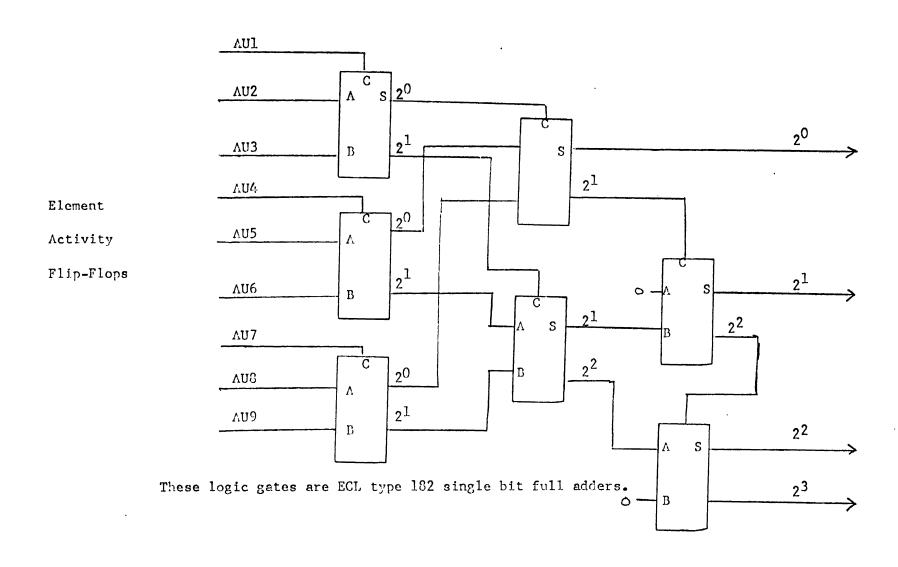

Shown in block diagram form in Figures 2.1 and 2.2, the AU was built on two boards named AU1 and AU2. With the exception of the input receivers, output drivers, and a data alignment network, the AU can be functionally described as being composed of an arithmetic and an element activity section.

The arithmetic section contains three working registers (A, B, and Q), an adder, and data input switches. The B register is not programmer accessible. The activity section contains a tag register, a stack (shift) register, and an element activity flip-flop. Also included is the necessary logic and switching which operate in conjunction with these components.

The register level diagram of the AU shows all of the main AU data paths and control. Not shown is the detail logic of functions such as the normalize decode network, zero and overflow detection, and the element activity. These items will be discussed in Section 4. The design is based on specific arithmetic algorithms described in Section 3.

Figure 2.1 AU Card 1

Figure 2.2 AU Card 2

#### 2.1 AU Registers

The AU contains the following registers and flip-flops visible to the programmer:

- A Register (PAAREG) Implicit operand in most instructions.

32 bits in length.

- Q Register (PAQREG) Quotient register for the divide instruction.

Used as a scratch register in the multiply instruction. 32 bits in length.

- Element Activity Flip-Flop (PAEACT) A one bit register used to indicate the state of the AU. If reset, the AU will not participate in the execution of most instructions.

- Activity Stack (PASTAK) A 21 bit FILO stack used to store the PAEACT bit. An attempt to push a bit out of the bottom of stack will send an error indication to the ICL.

- Tag Register (PATAGR) An Eight bit register used to hold a tag

loaded by the control unit. The tag can be used to permit or

inhibit the execution of instructions in the AU. Different AU

can contain different tags.

- Overflow Flip-Flop (PAOVFF) A one bit register used to indicate if an arithmetic overflow occurred within the AU. This flip-flop is sent as an error indicator to the ICL.

- Fault Flip-Flop (PAFALT) A one bit register used to completely

disable the entire Processing Element. Programmatically removes

PE from the Ensemble.

Other registers not visible to the programmer are:

- B Register (PABREG) Used to hold the explicit operand during most instructions. It holds the operand after receiving it from the control unit or the Element Memory. 32 bits in length.

- Shift Count Register (PASHCR) A six bit register used to hold

the shift amount. Possible values are +31 to -32 with positive

numbers indicating a right shift and negative numbers a left shift.

#### 2.2 AU Functional Units

Major functional units of the AU are:

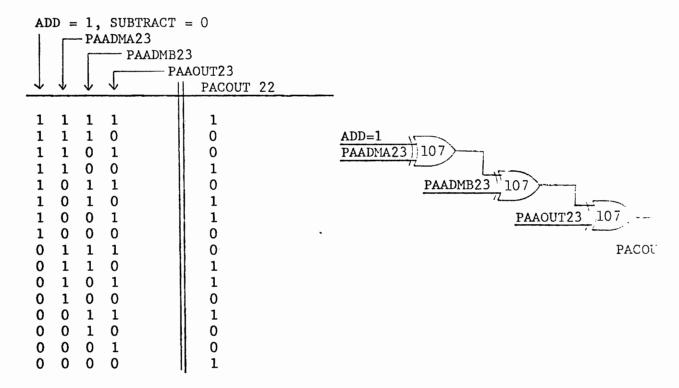

- Adder (PAADMN bits 23-0 and PAADEX for bits 31-24) A twos complement adder divided into a mantissa section and an exponent section. It is capable of both arithmetic and logical operations.

Output is PAAOUT.

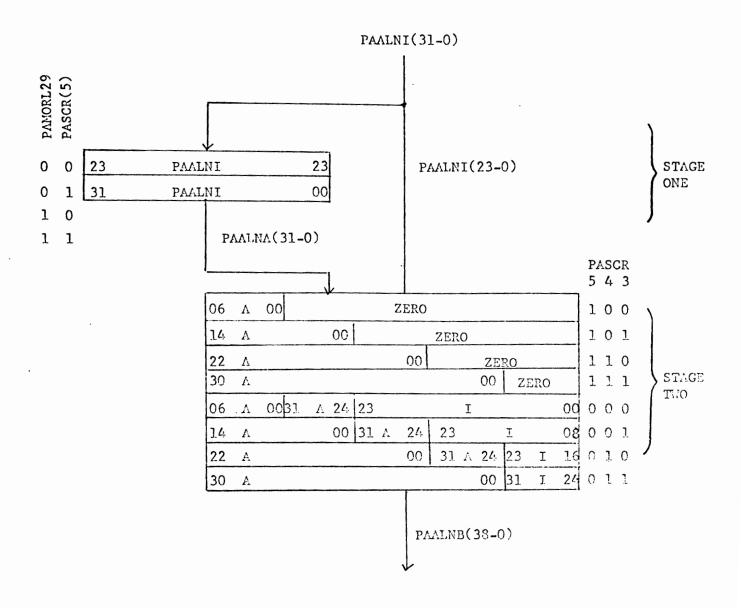

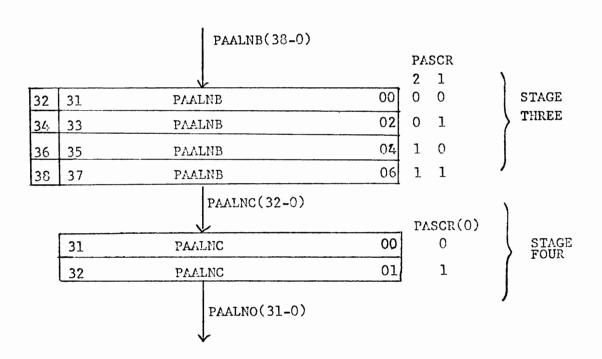

- Alignment Network (PAALNO) A 32 bit barrel shift network capable of 32 bit left and right logical shifts and 24 bit left and right arithmetic shifts. Input is PAALNI.

- Shift Count Two's Complement (PA2SCO) A six bit subtractor which subtracts PASHCR from zero. It is used to take a positive shift count and negate it to permit left shifts.

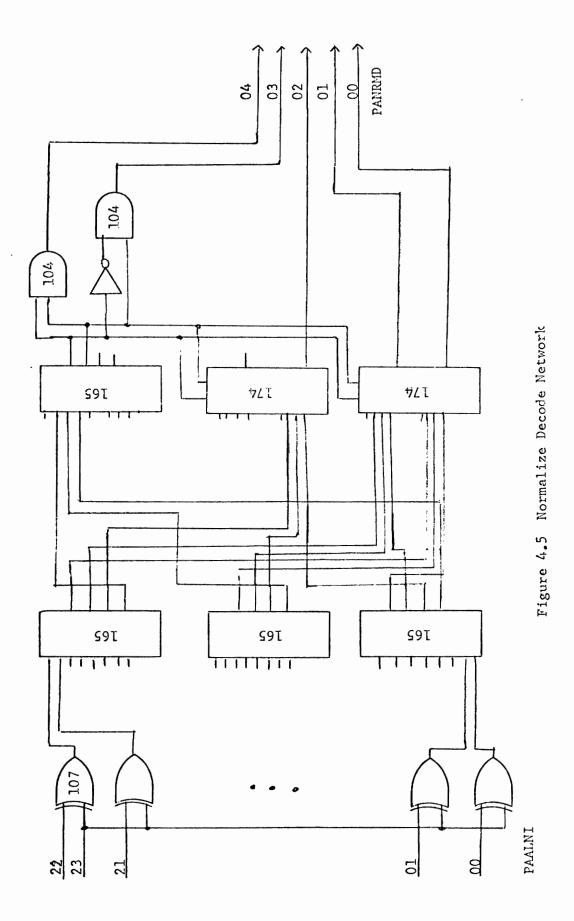

- Normalize Decode Network (PANRMD) A combinatorial network which counts the number of leading zeros or ones in a floating point fraction. Used to produce a count of 0 to 23 to left shift the fraction for normalization during floating point instructions.

Shift count output is PANRMD, a 5 bit positive value.

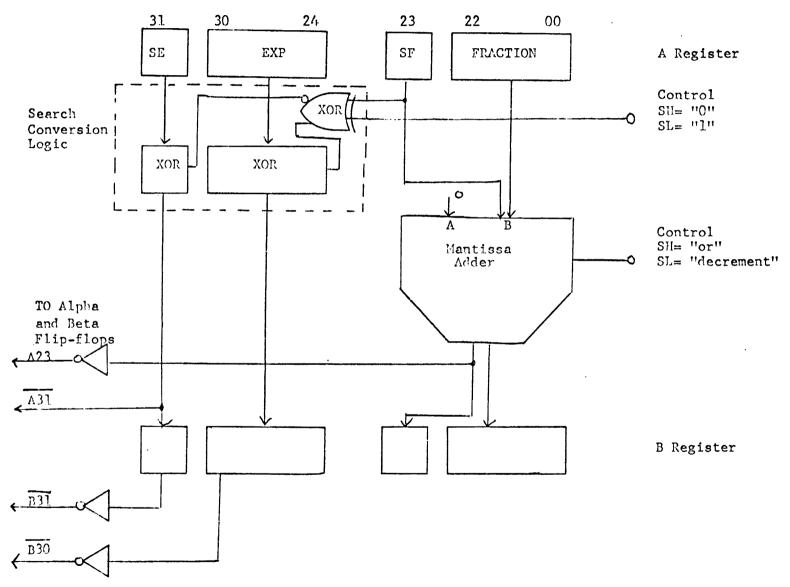

- Search Conversion Logic (PASRCH) Logic used in the conversion micro-step of the Select Highest/Lowest instructions.

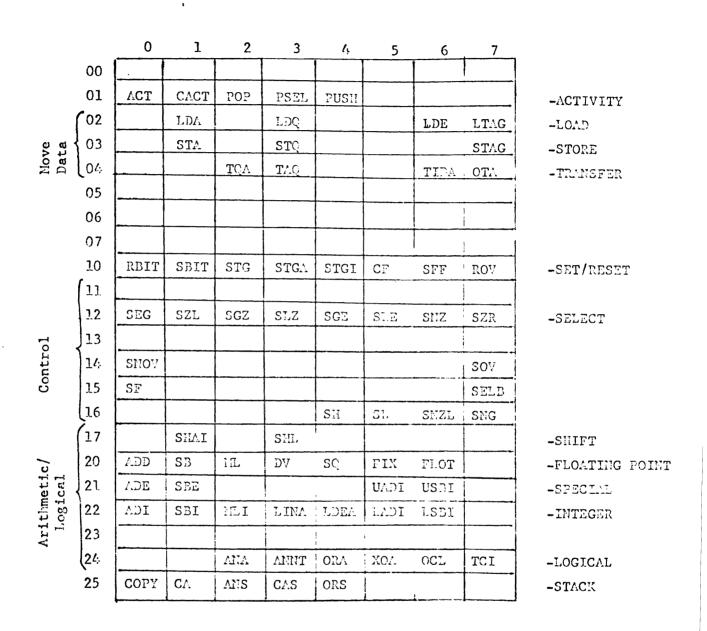

3.0 Instruction Set of the AU

The PEPE Arithmetic Unit can execute 71 Instructions that can be classified into six basic types:

- Activity those instructions which affect the Element Activity

Flip-Flop or Activity Stack.

- 2. Integer those instructions involved with the processing of integer data.

- Logical/Data Transfer those instructions involved with the processing of logical data.

- 4. Floating Point those instructions involved with the processing of floating point data.

- 5. Output those instructions which cause the AU to transmit data to the EM or the ACU.

- 6. Distributed those instructions which operate over a set of AU's rather than within a single AU.

Appendix C lists the instruction set in several different formats and classes each into one of the six types. The following sections will describe each type in general and will describe in detail the more interesting instructions of each type.

# 3.1 Activity Instructions

As mentioned in Section 2.0, the Element Activity (EA) Flip-Flop controls whether its particular AU will participate in the currently broadcast parallel instruction. Maximum use of this flip-flop is made to facilitate PEPE's associative nature. The select instructions cause the EA to set or reset depending on the result of an internal comparison between two pieces of data. For example, during Select on Not Equal Global (SNG-107), a comparison is made between a global operand and the AU A Register. The EA is reset in all AU performing an equal comparison.

# 3.2 Integer Instructions

#### 3.2.1 Single Integer

The AU integer instructions perform addition, subtraction and multiplication on the 24 bit integers described in Section 1.2.1.

The implicit operand is always the A Register. The explicit operand can be global or it can be fetched from the local EM. The Arithmetic Logic Unit (ALU) performs only addition. Subtraction is accomplished by complementing the subtrahend, introducing a carry into the lower order bit and then adding. Integer multiply is described in Section 3.4.3.

Instructions are: ADI

SBI

MLI

All AU integer instructions check for overflow. During addition, overflow is generated if the result sign is different than the two operand signs if they are the same. During subtraction, overflow is generated if the result sign is different than the minuend sign if the minuend sign is different from the subtrahend sign. The overflow signal is sent as an error interrupt to the ICL.

#### 3.2.2 Double Integer

The AU can process double integer values using a sequence of instructions. First, the lower words must be fetched. The operation can then be performed and the result stored. Then the upper words are fetched, operated on and stored. A flip-flop is used to store a borrow or carry between the lower and upper words.

Instructions are: LADI

LSBI

UADI

USBI

Overflow is checked when processing upper words.

# 3.3 Logical/Data Transfer Instructions

This class of instructions includes both those that perform logical (AND, OR) operations and those that cause the movement of data.

## 3.3.1 Logical Instructions

The AU performs logical instructions through the ALU. The A Register is one operand and the B Register is loaded with the other operand. As in most instructions the B data can be global or it can be fetched from the local EM. The result is placed in the A Register.

#### 3.3.2 Data Transfer Instructions

These instructions are classed as logical instructions because they handle data as 32 bit words without regard to their internal format. Data transfer can occur over the paths shown in Figure 3.1.

Instructions: LDA STGA

LDE STGI

LDQ TAQ

LTAG TIDA

SHL TQA

STG

Figure 3.1 User Controlled Data Paths

#### 3.4 Floating Point Instructions

This class of instructions make up the more interesting operations possible on PEPE. They operate on the PEPE floating point (FP) data representation described in section 1.2.4.

#### 3.4.1 Float/Fix

The Float instruction (FLOT) takes a 24 bit PEPE integer and converts it into a floating point number. This is done by normalizing and adding an exponent.

FLOT is performed in three steps as follows:

- Count leading "zeros" for positive numbers (leading "ones" for negative) starting at bit 22 down.

- 2. Shift the 24 bit integer the counted number of places left (filling with "zeros") thus normalizing it.

- 3. Subtract the count from 23 to form the exponent of the new FP number.

The subtraction from 23 is required because in the conversion, the binary point is moved 23 places from the right of bit 0 to the right of bit 23. All integers can be converted to FP.

The Fix (FIX) instruction is more complicated because not all FP numbers can be represented as integers. FIX takes a FP number and converts it to an integer. Consider that the PEPE FP number can be mathematically represented by:

$$+ M + X/Y$$

where M is a whole part and X/Y is the fraction part. FIX is defined to extract the whole part. For example:

| 5.3  | when | FIXed | becomes | 5  |

|------|------|-------|---------|----|

| 5.8  |      | ц     |         | 5  |

| -5.3 |      | **    |         | -6 |

| -5.8 |      | 11    |         | -6 |

The last two examples are so because -5.3 in two's complement form is really -6 + .7.

The FIX algorithm executes as follows:

- First check the exponent. If it is greater than 23, we cannot fix the number. An overflow indication is sent to the ICL.

- 2. Subtract the exponent from 23. Save this number as a shift count.

- 3. Shift the fraction right extending bit 23, the sign bit. Zero out the exponent.

- 4. If any significant bits were shifted out, add one to the new integer if it was negative.

The fourth step handles the two's complement negative numbers.

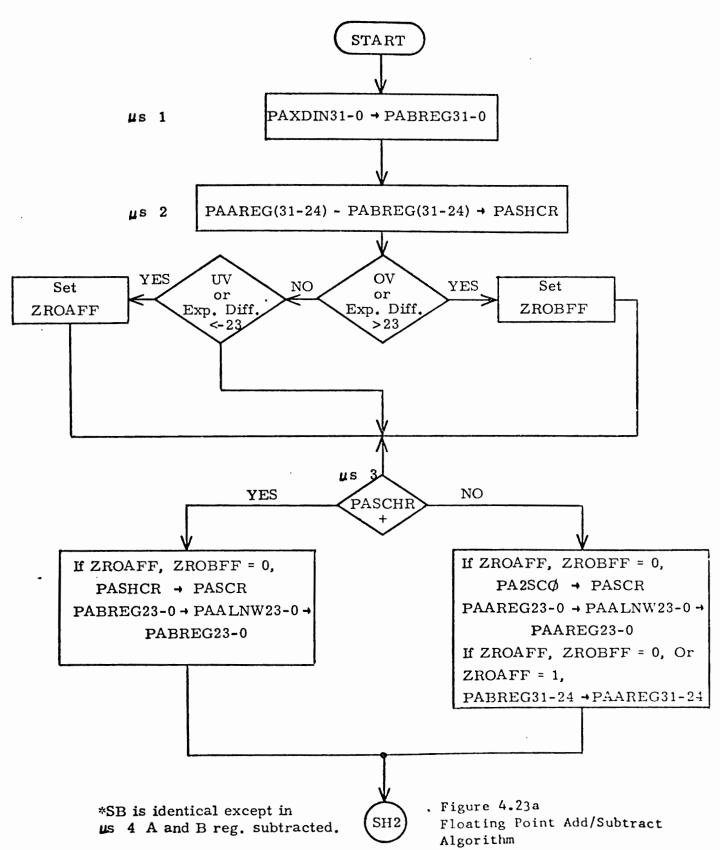

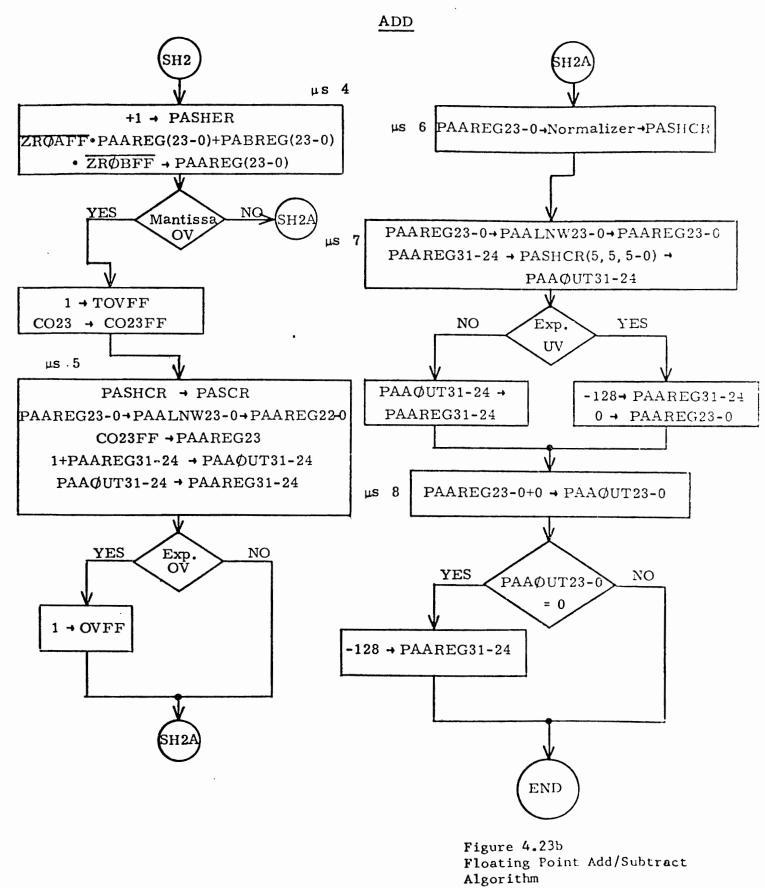

#### 3.4.2 Add/Subtract

FP add (ADD) and subtract (SB) are identical except for the actual arithmetic operation performed.

The ADD algorithm is:

- The two exponents are subtracted and the result is saved as a shift count.

- 2. The fraction with the smaller exponent is shifted in order to make the exponents equal.

- 3. The add or subtract is performed.

- 4. If the fraction sum overflows, an attempt is made to right shift the fraction and increment the exponent to correct the overflow.

- 5. If the exponent overflows, an error indication is sent to the ICL.

If the exponent difference is greater than 23, one of the fractions will be shifted completely out of the register. This is not an error condition but must be handled specially (because the shifter is not defined to operate with a greater than 23 arithmetic shift). The result of the

exponent subtraction is held in two flip-flops which cause the A or B input to the ALU to be zeroed during step 3.

An ADD example:

+

$$\frac{.1 \times 2^{30}}{.1 \times 2^{28}}$$

becomes: +  $\frac{.1 \times 2^{30}}{.001 \times 2^{30}}$

also:

+

$$\frac{.1 \times 2^{30}}{.1 \times 2^{1}}$$

becomes:  $\frac{.1 \times 2^{30}}{.0 \times 2^{30}}$

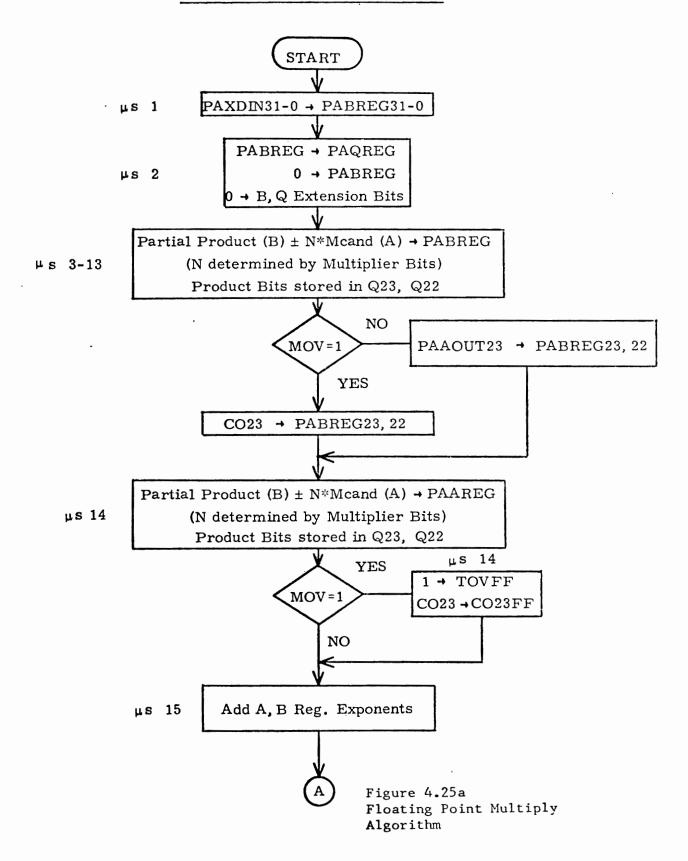

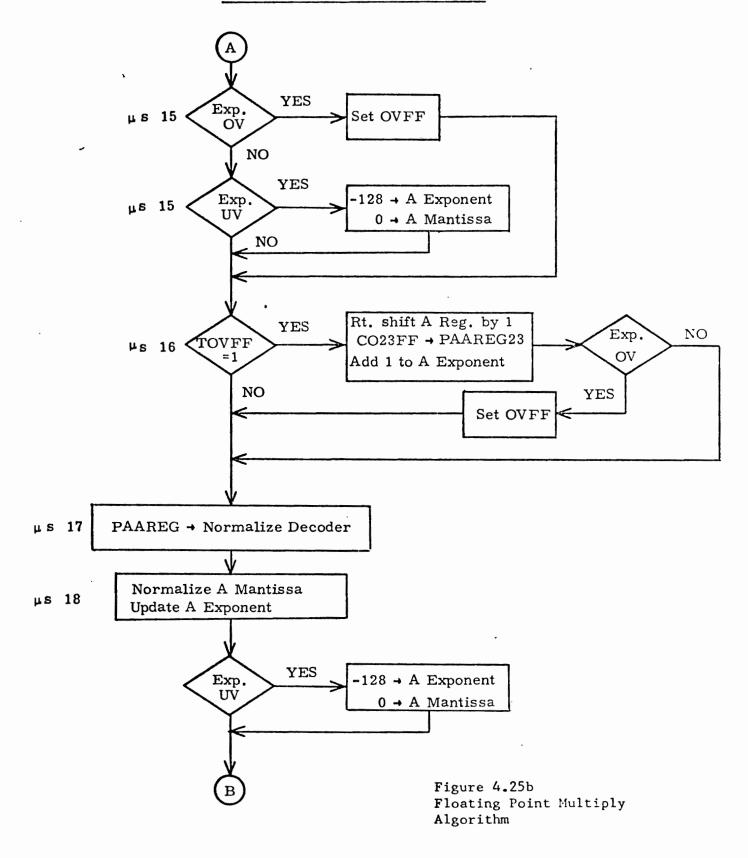

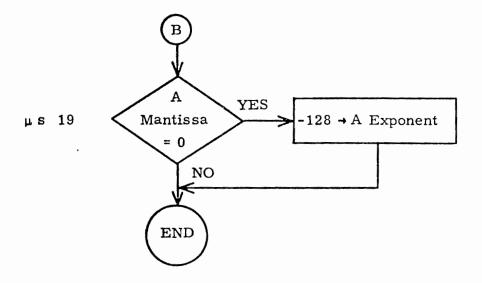

# 3.4.3 Multiply

Several multiply algorithms were considered for the AU.

The simplest is a bit by bit algorithm. That is, if a bit is "one" in the multiplier, add the multiplicand to a partial sum, shift it left one place and proceed to the next bit.

For example:

This method requires one step per bit in the multiplier. In the AU it would have required 24 steps.

A second method, as an extension of the first, is to take 2 bits of the multiplier at a time.

| multiplier bits | action                |       |     |

|-----------------|-----------------------|-------|-----|

| 00              | add O ,               | shift | two |

| 01              | add 1 X multiplicand, | shift | two |

| 10              | add 2 X multiplicand, | shift | two |

| 11              | add 3 X multiplicand, | shift | two |

Repeat this for each pair of bits in the multiplier.

For example:

This method needs one step per two bits in the multiplier and in the AU could operate in 12 steps. The major difficulty with this algorithm is the generation of the 3X multiplicand. O and 1X are easy to generate.

2X is just the multiplicand shifted left one place. We can, of course, get 3X by adding 1X and 2X but this adds a step to the execution.

The algorithm used in the AU is a modified version of the two bit multiply without the need for a 3X operand. The AU takes the two bits plus a "look ahead", one bit of the next pair. From these three bits add to the partial sum:

Thus, if we had a pair of bit groups as follows:

multiplier

$$0110 = 6$$

First, extend it right one zero bit and extend it to the left to complete the last group of three

0001100

-2

3

Group 1 100 -2 X

$$2^{\circ} = -2X$$

Group 2 011 2 X  $2^{2} = 8X$

Group 3 000 0 X  $2^{4} = 0X$

The result is 6 X the multiplicand. The first group served to correct by subtraction, what it knew was an average added by the second group. The 3 X operand becomes:

extend:

$$00110$$

$2$

Group 1 110 -1 X  $2^{\circ} = -1X$

Group 2 001 1 X  $2^{2} = 4X$

For our earlier example of 5 times 5:

Another example:

$$00101 = 5 \\

X 01110 = 14$$

Group 1 100 -2 X 2° = -2X

Group 2 111 0 X 2<sup>2</sup> = 0X

Group 3 001 1 X 2<sup>4</sup> = 16X

14X

This method, used in the AU, requires only 12 steps to perform the actual multiplication. The same algorithm operates correctly on both integer and floating point numbers.

# 3.4.4 Divide

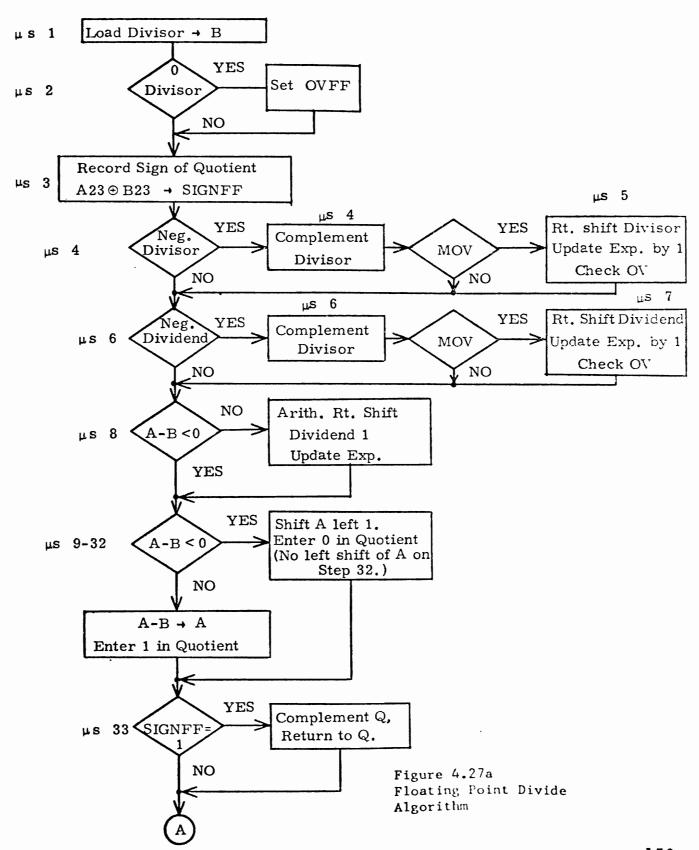

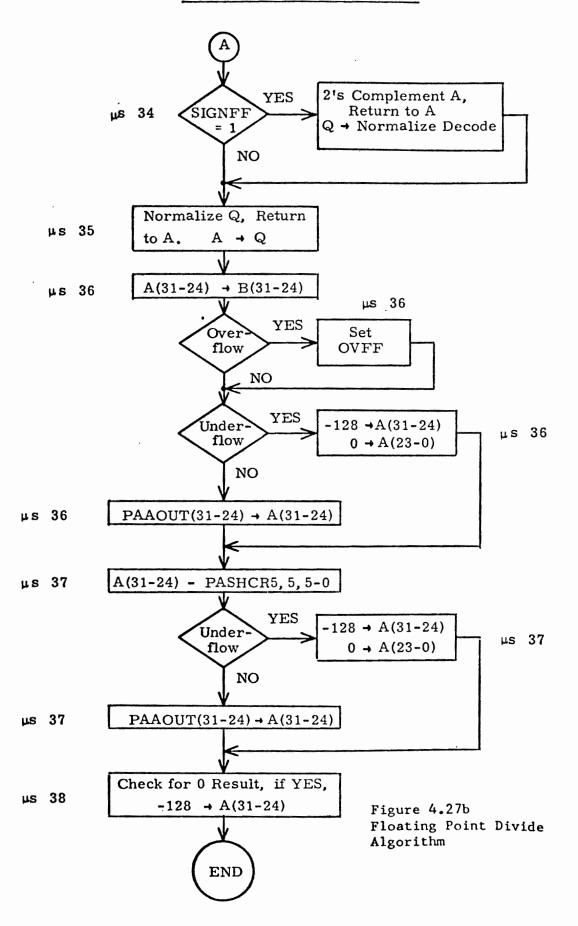

The AU divide (DV) algorithm resembles standard longhand division.

The algorithm divides positive numbers by positive numbers only. Therefore, the first thing the AU does is check if one or the other operand (but not both) are negative. If so, it sets a flip-flop to remember and then takes the two's complement of any negative operands. The AU also requires that the quotient be less than +1 (definition of normalized positive fractions). The AU checks this by subtracting the divisor from the dividend and examining the sign of the result.

For example:

0.11010

$$\div$$

0.10000

(13/16  $\div$   $\frac{1}{2}$  = 13/8)

0.11010  $\Rightarrow$  2's comp 0.11010

- 0.10000 subtraction: + 1.10000

0.01010

A negative result would indicate that the quotient will have a positive sign and a "one" in the MSB of the fraction (thereby less than +1). A positive result would indicate that the quotient will be greater than one (as in the example). To prevent this, the AU will shift the dividend one place right sign extended and increment the exponent by one. Then:

$$0.11010 \times 2^{\circ}$$

becomes  $0.01101 \times 2^{1}$

It is no longer normalized but the algorithm can handle that.

For the divide, the AU subtracts the corrected divisor from the dividend and follows these two rules: (by subtracting the divisor, the AU guesses that the quotient bit for this position is a "one").

- 1. If a "one" appears as the sign bit of the result of the subtraction, that means the guess of "one" as the quotient bit is incorrect. Therefore, the quotient bit is set to "zero", the result of the subtraction is discarded, and the dividend is shifted left zero fill one place.

- 2. If a "zero" appears as the sign bit of the result of the subtraction, the guess of "one" as the quotient bit is correct. Therefore, the quotient bit is set to "one" and the result of the subtraction is shift left zero fill one place to become the new dividend.

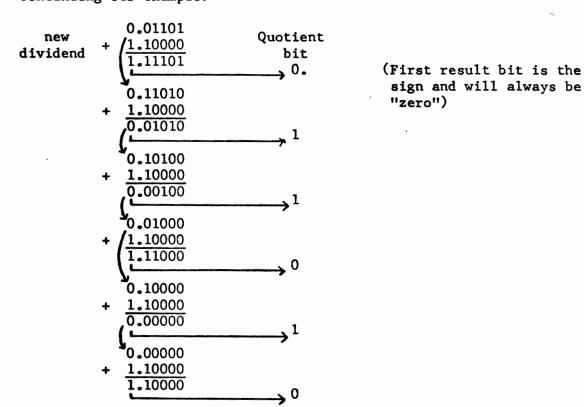

Continuing our example:

Quotient is 0.11010. The result exponent is the dividend exponent minus the divisor exponent. For the example it is 1 - 0 = 1. The final quotient is

$$0.11010 \times 2^{1} = 13/16 \times 2^{1} = 13/8$$

The AU executes the iterative portion of the DV instruction in 24 steps.

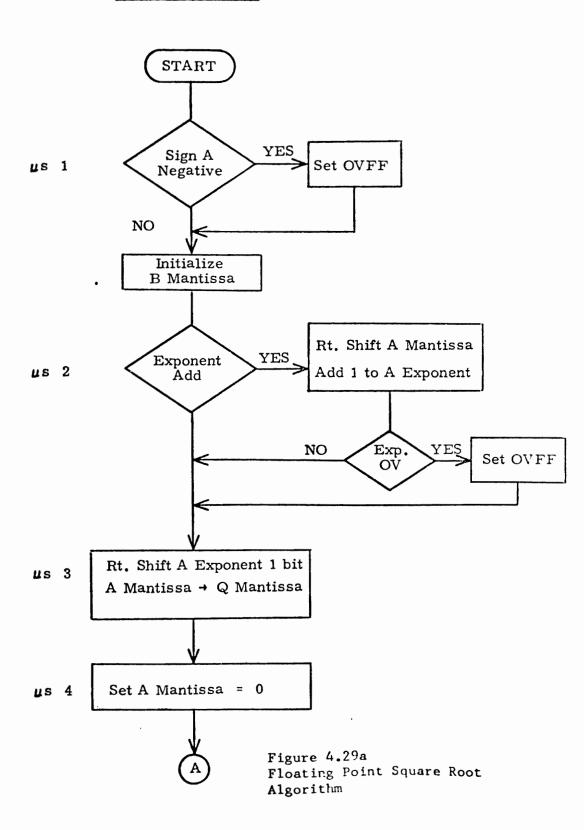

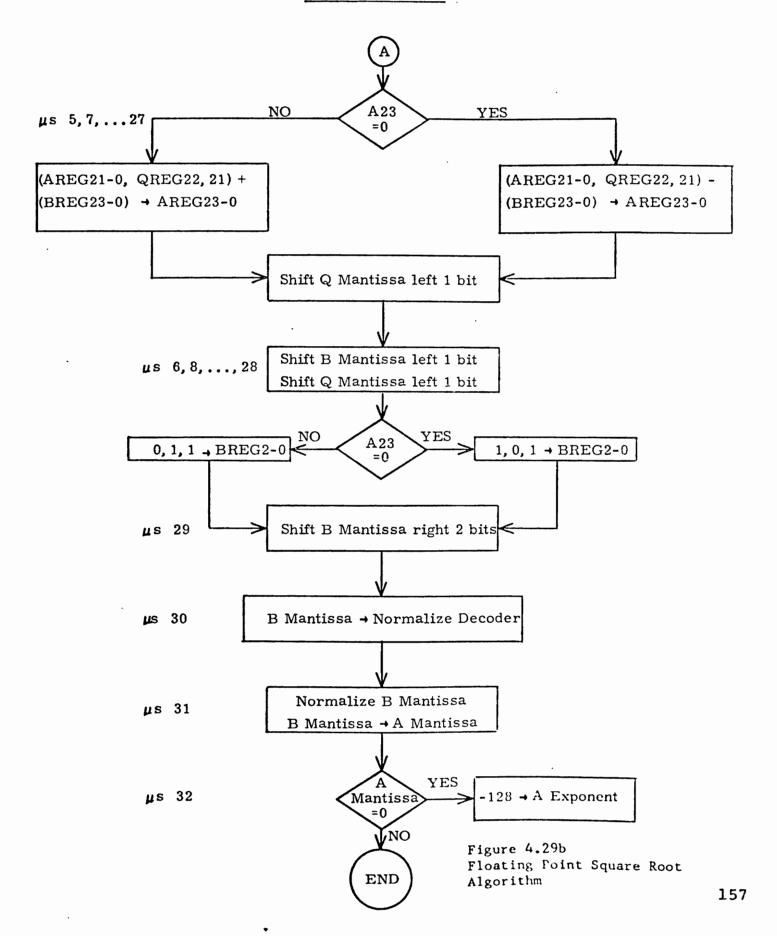

# 3.4.5 Square Root

In base ten, a square root operation is a set of guesses and subtractions. The guess can be 0 to 9. In longhand decimal

If the guess of the root digit was too high as evidenced by a negative difference, the digit is decremented by one to become a new guess. The AU also guesses at the result, but in binary only two guesses are possible.

A longhand example in binary (Example A):

| G           | 1  | 1         | 0  | 1  | 1  | 1  | A12        |

|-------------|----|-----------|----|----|----|----|------------|

|             | 10 | 11        | 11 | 01 | 10 | 10 |            |

| 1 X 1       | -1 |           |    |    |    |    |            |

|             | 1  | 11        |    |    |    |    | A1         |

| 101 X 1     | -1 | 01        |    |    |    |    | A2         |

|             |    | 10        | 11 |    |    |    | A3         |

| 1100 X 0    |    | <u>-0</u> | 00 |    |    |    | A4         |

|             |    | 10        | 11 | 01 |    |    | A5         |

| 11001 X 1   |    | <u>-1</u> | 10 | 01 |    |    | <b>A</b> 6 |

|             |    | 1         | 01 | 00 | 10 |    | A7         |

| 110101 X 1  |    | <u>-0</u> | 11 | 01 | 01 |    | A8         |

|             |    |           | 01 | 11 | 01 | 10 | A9         |

| 1101101 X 1 |    |           | -1 | 10 | 11 | 01 | A10        |

|             |    |           | 0  | 0  | 10 | 01 | A11        |

|             |    |           |    |    |    |    | Reference  |

|             |    |           |    |    |    |    | Line #     |

The AU guesses that each root bit is a "one", then performs a subtraction. If the guess turns out to be incorrect, the subtraction result

is still used but a correction factor is added during the next subtraction.

The AU proceeds as follows:

First, the exponent must be even. If it is not, the fraction is shifted right one place sign extended and one is subtracted from the exponent.

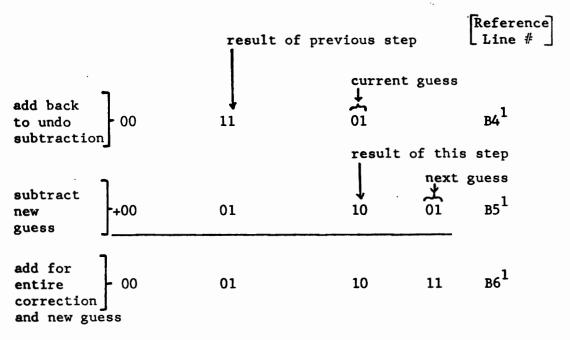

The first two bits of the square are taken. A guess is made that the first bit of the result will be a "one". The guess is subtracted from the operand This result becomes the new operand and is concatenated with the next two bits of the square. The guess is then shifted left one place and the lower three bits are replaced by:

- 011 if the subtraction is negative

- 101 if the subtraction is positive.

This becomes the new guess. If the result of the last subtraction was negative, we add the new guess else we still subtract it. The process continues until all bits of the square are used. The root is contained in the last guess word. It is normalized and the exponent is shifted right one place sign extended to divide it by two and the instruction is complete.

| earlier examp  | le:             |    |     |    | Reference<br>Line # |

|----------------|-----------------|----|-----|----|---------------------|

| $\sqrt{10}$ 11 | 11              | 01 | 10  | 10 | -                   |

| -01 ← fir      | st gues         | s  |     |    |                     |

| 01 11          |                 |    |     |    | B1                  |

| <b>-01</b> 01  |                 |    |     |    | B2                  |

| 10             | 11              |    |     |    | в3,                 |

| -11            | 01              |    |     |    | B41                 |

| 11             | 10              | 01 |     |    | B5 1                |

| + 01           | 10              | 11 |     |    | B6 <sup>1</sup>     |

| 01             | 01              | 00 | 10  |    | в7                  |

| -00            | 11              | 01 | 01_ |    | в8                  |

|                | 01              | 11 | 01  | 10 | в9                  |

|                | <u>-01</u>      | 10 | 11_ | 01 | B10                 |

|                |                 | 00 | 10  | 01 | B11                 |

| last guess —   | <del>&gt;</del> | 11 | 01  | 11 | B12                 |

|                |                 |    |     |    |                     |

| normalize      |                 |    |     |    |                     |

| 0.110111       |                 |    |     |    |                     |

In line A4 of the longhand method, zero was subtracted because a guess of zero was used as the next bit of the answer. In line B4<sup>1</sup> of the algorithm, a guess of "one" was subtracted (since the algorithm always guesses "one") and as seen in line B5<sup>1</sup>, a negative result indicates too large of a guess. Line B6<sup>1</sup> applies the following insertion factor which replace the last three bits of the guess:

Two's complement of the new guess

Correct bit of the root.

The two's complement of the new guess serves to correct the over subtraction of this step during the next step. The "correction" field used as a result of a correct guess is:

New guess

Correct bit of the root.

In the example, the algorithm subtracted:

and produced a negative result. Therefore it must add this back during the next step while at the same time subtracting the new guess word.

The AU executes the iterative portion of the square root instruction in 24 steps.

# 3.5 Output Instructions

### 3.5.1 Store Instructions (STA)

All of the AU visible registers can be stored in Element Memory.

During a single micro-step, the selected data is gated to the EM and

written. Storable register are:

A Register

Q Register

Activity Stack

Tag Register

EA Flip-Flop

Overflow Flip-Flop

# 3.5.2 Output A Register Instruction (OTA)

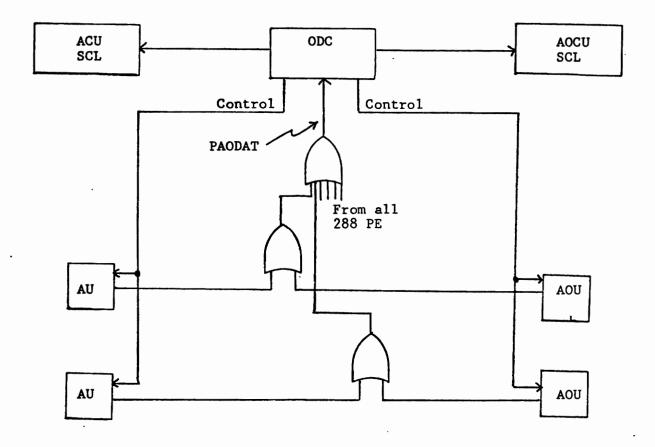

A special instruction which executes both in the SCL and AU is used to retrieve a 32 bit word from one AU and place it in the SCL A Register. In preparation for the execution of an OTA instruction, appropriate select instructions should have been executed to leave only one AU active. When the SCL decodes an OTA, it sends a copy to the PICU while at the same time requesting use of the Output Data Bus (ODB) from ODC, Figure 3.2. When a bus cycle is granted, the AU gates its A Register onto the bus. After some signal propagation delay, the ODC responds to the SCL with a data ready line and the correct data.

The PAODAT Bus is 32 bits wide

Figure 3.2 Output Data Bus/OTA Instruction Block Diagram

#### 3.6 Distributed Logic Instructions

PEPE also includes a set of logic called distributed logic. This logic is not contained in any one PEPE unit but is spread over the control console and the element bays.

#### 3.6.1 Count AU

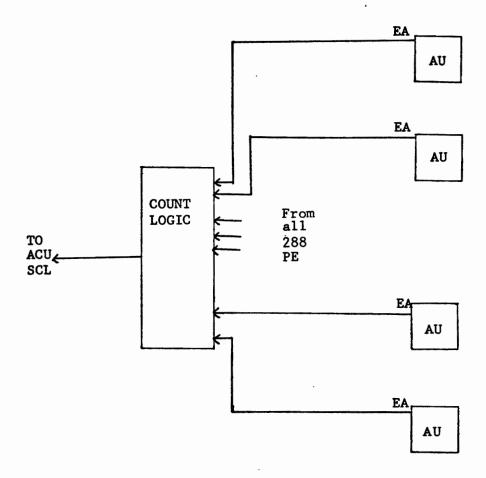

The SCL may at any time, request a count of the number of AU is with their EA Flip-Flops on. Special logic exists within each EB and the CC to perform this count. Shown in Figure 3.3, each AU in the ensemble presents the state of its EA to the count logic. The count logic presents a nine bit (0-288) count to the SCL which can be loaded into the SCL A Register during the execution of a Read Activity (RDA) instruction. The AU does not directly participate in this instruction.

Two other signals are generated by the AU Count logic. They are SAMANY and SAACTV. The signal SAMANY is a detection of activity count greater than one or "many" active. The signal SAACTV is also a detection of activity count, here for a count greater than zero. Both of these signals are transmitted to the SCL and SAMANY is also sent to the PICU.

# 3.6.1 Select Highest/Lowest Instructions

A need was identified in PEPE for a high speed algorithm to perform a maximum or minimum search over a set of data values in the element ensemble. The two search instructions are Select Highest and Select Lowest (SH/SL). The SH/SL instructions execute as follows: in the set of active AU's, reset element activity in each AU whose "A" Register contains a nonmaximal/minimal value relative to the set of active AU. This value comparison is done for the set of PEPE integer or normalized floating point numbers but never for a mix of both types.

Figure 3.3 Count AU Block Diagram

A discussion of valid operands for the SH/SL may be appropriate here. For simplicity, consider a machine with eight bit registers instead of 32 bit registers. Let four bits represent the fraction or integer and four bits represent the exponent. See figure 3.4. Note that the entire discussion following can be directly extrapolated to PEPE 24 bits fraction/integer and eight bit exponent.

When doing a search over a set of integers, SH/SL requires that the exponent and the sign of the exponent be zero. The integer value is searched for the largest/smallest value.

A search over a set of floating point numbers requires that the fraction be normalized. Normalized numbers are those whose SF and most significant bit of the fraction are different. As shown in figure 3.4, + 1/8 is not a valid floating point number for this reason. If + 1/8 were permitted, the numbers 0010 0001 and 0000 0100 would both have the value of  $+ \frac{1}{2}$ . The search algorithm as described later will report that the first binary pattern is larger than the second when they are actually equal.

Also note that the value of floating point zero can be represented in 16 different ways, that is with any exponent as long as the fraction and SF are all zero. In effect 0111 0000 = 0000 0000 = 1000 0000. Therefore, we define floating point zero to be the "smallest" zero representable or 1000 0000 which is 0 X  $2^{-8}$ . Note that floating point zero is not normalized.

| 7  | 6 | 5   | 4 | 3  | 2 1 0    |                |

|----|---|-----|---|----|----------|----------------|

| 0  | 0 | 0   | 0 | SI | VALUE    | INTEGER        |

|    |   |     |   |    |          |                |

| SE |   | EXP |   | SF | FRACTION | FLOATING POINT |

TWO'S COMPLEMENT NOTATION

|      |           | INTERPRETATION |                        |              |  |

|------|-----------|----------------|------------------------|--------------|--|

| SIGN | MAGNITUDE | INTEGER        | EXPONENT               | FRACTION     |  |

| 0    | 1 1 1     | +7             | 2 <sup>7</sup> =128    | +7/8         |  |

| 0    | 1 1 0     | +6             | 2 <sup>6</sup> =64     | +3/4         |  |

| 0    | 101       | +5             | 2 <sup>5</sup> =32     | +5/8         |  |

| 0    | 100       | +4             | 2 <sup>4</sup> =16     | +1/2         |  |

| 0    | 0 1 1     | +3             | 2 <sup>3</sup> =8      | +3/8 *       |  |

| 0    | 0 1 0     | +2             | 2 <sup>2</sup> =4      | +1/4 *       |  |

| 0    | 0 0 1     | +1             | 2 <sup>1</sup> =2      | +1/8 *       |  |

| 0    | 000       | . 0            | 20=1                   | 0            |  |

| 1    | 111       | -1             | 2 <sup>-1</sup> =1/2   | -1/8 *       |  |

| 1    | 110       | -2             | 2 <sup>-2</sup> =1/4   | -1/4 *       |  |

| 1    | 101       | <b>-</b> 3     | 2 <sup>-3</sup> =1/8   | -3/8 *       |  |

| 1    | 100.      | _4             | 2 <sup>-4</sup> =1/16  | -1/2 *       |  |

| 1    | 011       | -5             | 2 <sup>-5</sup> =1/32  | <b>-</b> 5/8 |  |

| 1    | 0 1 0     | -6             | 2 <sup>-6</sup> =1/64  | -3/4         |  |

| 1    | 001       | -7             | 2 <sup>-7</sup> =1/128 | <b>-</b> 7/8 |  |

| 1    | 000       | -8             | 2 <sup>-8</sup> =1/256 | -1           |  |

|      |           |                |                        |              |  |

\* Not Valid Normalized Floating Point Patterns

Figure 3.4 A Four Bit Number System

## 3.6.2.1 Algorithm

The algorithm to be described executes in the AU and requires a maximum of 35 100 ns micro-steps. Execution consists of two parts, Conversion and Search.

### 3.6.2.2 Conversion

The first micro-step of SH/SL converts the set of values to be compared from the valid set of PEPE 2's complement number system into an ordered set of operands. This conversion is a mapping of PEPE numbers onto a 32 bit pure magnitude number line. In the case of Select Highest, the largest (most positive) PEPE number is converted to all ones and the smallest (most negative) PEPE number is converted to all zeros. For Select Lowest the mapping is reversed.

For the purposes of this explanation, the set of PEPE floating numbers is broken into 4 classes. Refer to figure 3.5. Column 1 represents the ordered set of 2's complement normalized PEPE operands. Top-most positive, bottom-least positive. Fraction sign (bit 23) is first and exponent sign bit 31 next, for both, 0 is positive. The exponent field (bits 30 to 24) is next. Fraction field is last (bits 22 to 0). The classes are:

Class 1 contains all operands with positive fraction and

positive exponent.

Class 2 contains all operands with positive fraction and negative exponent.

Note the zero operand is the least class 2 element. Class 3 contains all operands with negative fraction and negative exponent. Here the exponent field is ordered all zeros to all ones. The fraction field is ordered by normalized negative values (zero with all ones to all zeros). This puts the operands in order (most to least positive) but not in decreasing binary

| _ | Flo<br>Poi | ati<br>nt<br>ber | ng           | Highes<br>Mapping |                          | Lowest     | g .                       |         |

|---|------------|------------------|--------------|-------------------|--------------------------|------------|---------------------------|---------|

|   | SF         | SE               | EXP FRAC     | SF SE             | EXP FRAC                 | SF SE      | EXP FRAC                  |         |

|   | 0          | 0                | 1 - 1 11 - 1 | 1 1               | 1 - 1 11 - 1             | 0 0        | 0 - 0 00 - 0              |         |

|   | 0          | 0                | 1 - 1 10 - 1 | 1 1               | 1 - 1 10 - 0             | 0 0        | 0 - 0 01 - 1              | CLASS 1 |

|   | 0          | 0                | 0 - 0 11 - 1 | 1 1               | 0 - 0 11 - 1             | 0 0        | 1 - 1 00 - 0              | OLADO 1 |

|   | 0          | 0                | 0 - 0 10 - 0 | 1 1               | 0 - 0 10 - 0             | 0 0        | i - 1 01 - 1              |         |

|   | 0          | 1                | 0 - 0 10 - 0 | 1 1               | 0 - 0 10 - 0             | 0 1        | 0 - 0 00 - 0              |         |

|   | 0          | 1                | 1 - 1 10 - 0 | 1 0               | 1 - 1 10 - 0             | 0 1        | 0 - 0 01 - 1              | CLASS 2 |

| ١ | 0          | 1                | 0 - 0 11 - 1 | 1 0               | 0 - 0 11 - 1             | 0 1        | 1 - 1 00 - 0              | CLASS 2 |

|   | 0          | 1                | 0 - 0 10 - 0 | 1 0<br>1 0        | 0 - 0 10 - 0 0 - 0 0 - 0 | 0 1<br>0 1 | 1 - 1 01 - 1 1 - 1 11 - 1 | (ZERO)  |

|   | 1          | 1                | 0 - 0 01 - 1 | 0 1               | 1 - 1 01 - 1             | 1 0        | 0 - 0 10 - 0              | ,==,    |

|   | 1          | 1                | 0 - 0 00 - 0 | 0 1               | 1 - 1 00 - 0             | 1 0        | 0 - 0 11 - 1              | CLASS 3 |

|   | 1          | 1                | 1 - 1 01 - 1 | 0 1               | 0 - 0 01 - 1             | 1 0        | 1 - 1 10 - 0              | OLASS 3 |

|   | 1          | 1                | 1 - 1 00 - 0 | 0 1               | 0 - 0 00 - 0             | 1 0        | i - 1 11 - 1              |         |

| ľ | 1          | 0                | 0 - 0 01 - 1 | 0 0               | 0 - 0 00 - 0             | 1 1        | 0 - 0 10 - 0              |         |

|   | 1          | 0                | 0 - 0 00 - 0 | 0 0               | 1 - 1 00 - 0             | 1 1        | 0 - 0 11 - 1              | CLASS 4 |

|   | 1          | 0                | 1 - 1 01 - 1 | 0 0               | 0 - 0 01 - 1             | 1 1        | 1 - 1 10 - 0              | ODAGO 4 |

|   | 1          | 0                | 1 - 1 00 - 0 | 0 0               | 0 - 0 00 - 0             | 1 1        | i - 1 11 - 1              |         |

Select

Select

Original

Figure 3.5 Number Classes and Conversion Floating Point

sequence. Class 4 contains all operands with negative fraction and positive exponent. It is ordered similarly to class 3. Column 2 shows the converted values for select highest and Column 3 shows the converted values for select lowest.

The set of PEPE integers is broken into 2 classes. Refer to figure 3.6. Column 1 represents the ordered set 2's complement PEPE integers: top-most positive, bottom-least positive. Fraction sign (bit 23) is first, zero is positive. Exponent sign and exponent are all zero. Fraction field is last (bits 22 to 0). The classes are:

Class 1 contains all positive integers.

Class 2 contains all negative integers.

Column 2 shows converted values for SH, and column 3 shows the converted values for SL. Operation of SH/SL on integer values can be considered a subset of floating point operation when the exponent is zero.

Rules for either floating point or integer conversion are:

## Select Highest (SH)

- 1. Complement bit 31 if bit 23 equals zero

- 2. Complement bits (30-24) if bit 23 equals one

- 3. Bits (22-0) remain unchanged

- 4. Complement bit 23

# Select Lowest (SL)

- 1. Complement bit 31 if bit 23 equals one

- 2. Complement bits (30-24) if bit 23 equals zero

- 3. Complement bits (22-0)

- 4. Bit 23 remains unchanged

| Original<br>Integer<br>Number |       |                                               | Highe          | Select<br>Highest<br>Mapping |                     |        | ect<br>est<br>ping |     |                                    |                                      |         |

|-------------------------------|-------|-----------------------------------------------|----------------|------------------------------|---------------------|--------|--------------------|-----|------------------------------------|--------------------------------------|---------|

| SI                            | XX    | XXX                                           | INT            | SI XX                        | XXX                 | INT    | SI                 | XX  | XXX                                | INT                                  |         |

| 0 0                           | 0 0   | 0 - 0 1<br>0 - 0 1<br>1<br>0 - 0 0<br>0 - 0 0 | 1 - 0<br>0 - 1 | 1 1<br>1 1<br>1 1<br>1 1     | 0 - 0               | 11 - 0 | 0 0 0              |     | 1 - 1 0<br>1 - 1 0<br>:<br>1 - 1 1 | 00 - 1                               | CLASS 1 |

| 1<br>1<br>1                   | 0 0 0 | 0 - 0 1<br>0 - 0 1<br>0 - 0 0<br>0 - 0 0      | 1 - 0<br>0 - 1 | 0 0                          | 1 - 1<br>;<br>1 - 1 |        | 1<br>1<br>1        | 1 ( | ) - 0 (<br>;<br>) - 0 ;            | 00 - 0<br>00 - 1<br>11 - 0<br>11 - 1 | CLASS 2 |

Figure 3.6 Number Classes and Conversion Integer

The conversion is done in the ALU of the element. Following this mapping, each element contains a value in pure 32 bit magnitude representation with the same relative "value" as the original PEPE number. All that remains is to compare this value in all active elements and leave the element(s) with the maximum/minimum value active.

#### 3.6.2.3 Search

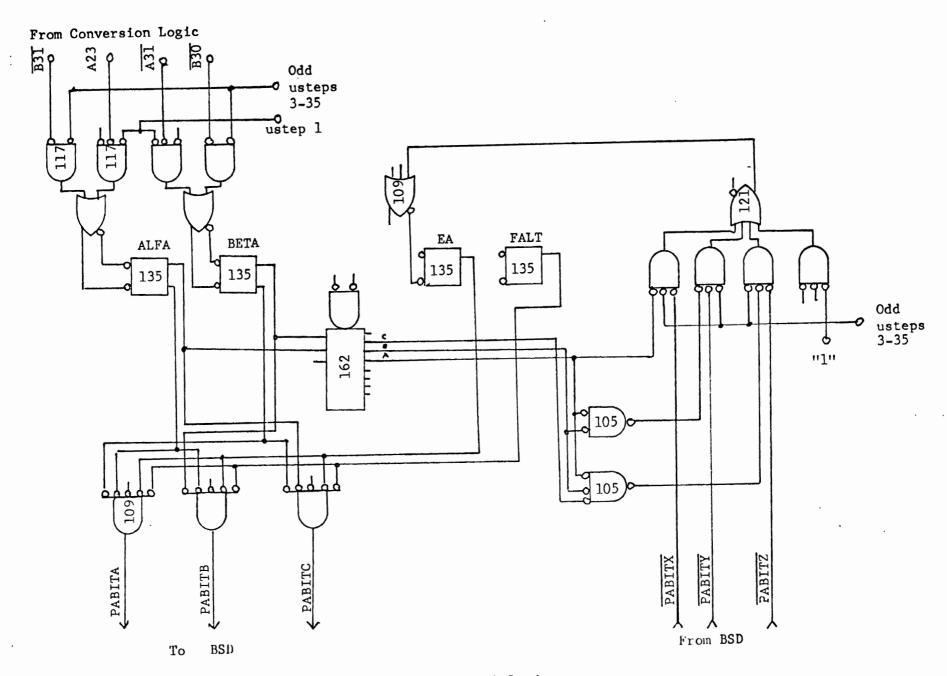

Figure 3.7 illustrates the basic principle behind the search function. One bit of the converted value in each active element is gated out of the element and into the Signal Distribution System (SDS). The SDS in PEPE is that portion of logic that enables the control console and the element bays to communicate. The SDS can be considered to encompass the distributed logic. In the SDS, they are "OR"ed together and transmitted back to each element. The line sent back to each element indicates that at least one of the active elements has a "l" in the bit position being examined. A decision is then made in each element to reset the element activity if that element has a "O" in the bit position and at least one element has a "l". It is clear that any element with a "l" in a particular bit position has a number of greater magnitude than an element with a "O" in that position.

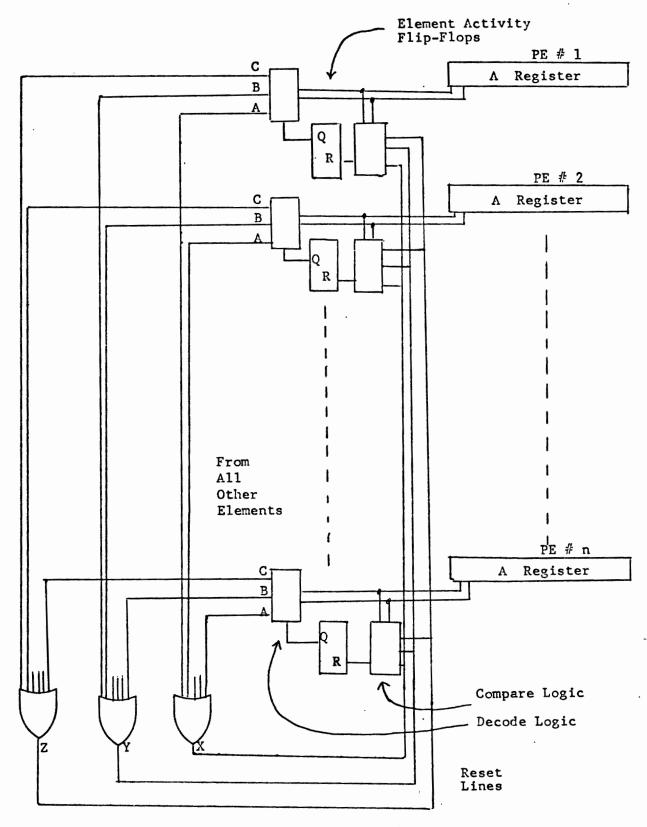

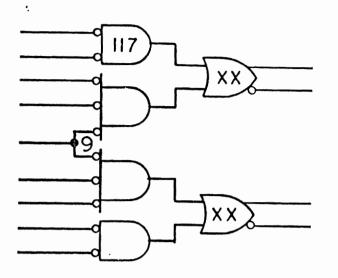

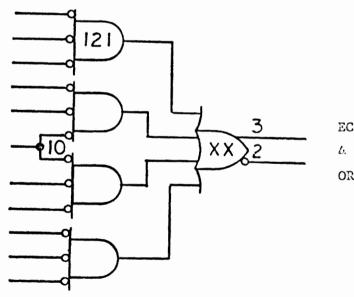

Due to PEPE layout constraints, the propagation delay encountered in the "OR" circuit will be on the order of 200 ns. Therefore one bit each 200 ns is the maximum rate in the "OR" circuit and a SH/SL operation over the full 32 bit word would take 6400 ns. In order to reduce this time, the method in Figure 3.8 was used. Two bits each 200 ns are output by the element for a search time of 3200 ns.

Figure 3.7 SH/SL One Bit Per Cycle

Figure 3.8 shows that 2 bits are decoded and sent out of the element on 3 lines. Each of the 3 lines from all of the elements are "OR"ed and returned to the element. If the element has 2 bits that are less than indicated by the 3 reset lines, the element resets its element activity. Figure 3.9 shows the truth table for this reset function. 🗸 and 😝 are the 2 bits being examined, A, B and C are the 3 output lines of the element, **X,** Y and Z are the 3 "OR"s of all the elements A, B and C lines, and RESET is the signal to reset the element activity flip-flop. Line A equals "1" when both bits being examined are binary "1". Line B equals "1" when the high order bit is a "1" and the low order bit is a "0". Line C equals 1 when the low order bit is a "1" and the high order bit is a "0". All 3 lines are "0" when both bits are zero. These 3 lines are "OR"ed in the CSD/BSD with the corresponding lines from all the other active elements and these 3 signals are returned to every element. The element then compares its local A, B, C lines with the global X, Y, Z lines and any elements whose ABC lines indicate its 2 bits are less than the XYZ lines show for the entire system, will reset its element activity.

Figure 3.8 SH/SL Two Bits Per Cycle

A,B,C Lines Truth Table

| ALPIIA | BETA | A | В | С |

|--------|------|---|---|---|

| .0     | 0    | 0 | 0 | 0 |

| 0      | 1    | 0 | 0 | 1 |

| 1      | 0    | 0 | 1 | Q |

| 1      | 1    | 1 | 0 | 0 |

$A = ALPHA \cdot BETA$

$B = ALPHA \cdot \overline{BETA}$

$C = \overline{ALPHA} \cdot BETA$

Reset Element Activity Truth Table

| Keser Fre | ement. | ACCI | VIL | <i>,</i> - | Lut |   | anie |             |

|-----------|--------|------|-----|------------|-----|---|------|-------------|

| ALPHA     | BETA   | Λ    | В   | С          | Х   | Y | Z    | RESET       |

| 0         | 0      | 0    | 0   | 0          | 0   | 0 | 0    | 0           |

| 0         | 0      | 0    | 0   | 0          | 0   | 0 | 1    | 1           |

| 0         | 0      | 0    | 0   | 0          | 0   | 1 | 0    | 1           |

| 0         | 0      | 0    | 0   | 0          | 0   | 1 | 1    | 1           |

| 0         | 0      | 0    | 0   | 0          | 1   | 0 | 0    | 1<br>1<br>1 |

| 0         | 0      | 0    | 0   | 0          | 1   | 0 | 1    |             |

| 0         | 0      | 0    | 0   | 0          | 1   | 1 | 0    | 1           |

| . 0       | 0      | 0    | 0   | 0          | 1   | 1 | 1    | 1           |

| 0         | 1      | 0    | 0   | 1          | 0   | 0 | 1    | 0           |

| 0         | 1      | 0    | 0   | 1          | 0   | 1 | 1    | 1           |

| 0         | 1      | 0    | 0   | 1          | 1   | 0 | 1    | 1           |

| . 0       | 1      | 0    | 0   | 1          | 1   | 1 | 1    | 1           |

| 1         | 0      | 0    | 1   | 0          | 0   | 1 | 0    | 0           |

| 1<br>1    | 0      | 0    | 1   | 0          | 0   | 1 | 1    | 0           |

| 1         | 0      | 0    | 1   | 0          | 1   | 1 | 0    | 1           |

| 1         | 0      | 0    | 1   | 0          | 1   | 1 | 1    | 1           |

| 1         | 1      | 1    | 0   | 0          | 1   | 0 | 0    | 0           |

| 1         | 1      | 1    | 0   | 0          | 1   | 0 | 1    | 0           |

| 1         | 1      | 1    | 0   | 0          | 1   | 1 | 0    | 0           |

| 1         | 1      | 1    | 0   | 0          | 1   | 1 | 1    | 0           |

|           |        |      |     |            |     |   |      | !!          |

$RESET = \overline{A}X + \overline{A}\overline{B}Y + \overline{A}\overline{B}\overline{C}Z$

Figure 3.9 Search: Reset Element Activity Function

The flip-flops  $\propto$  and  $\theta$  contents are as follows during execution of SH/SL:

| u-step<br>1<br>2                     | 0<br>A23*  | Q<br>0<br>B31 | conversion micro-step                                           |

|--------------------------------------|------------|---------------|-----------------------------------------------------------------|

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | в30        | B29           |                                                                 |

| 6                                    | B28        | B27           |                                                                 |

| 8<br>9                               | В26        | B25           |                                                                 |

| 10<br>11                             | B24        | B23*          | ·                                                               |

| 12<br>13                             | B22        | B21           |                                                                 |

| 14<br>15                             | В20        | В19           | *Note that the effective bit 23                                 |

| 16<br>17                             | B18        | B17           | is examined twice. This was done to simplify the SH/SL logic.   |

| 18<br>19                             | B16        | В15           | The second pass of bit 23 through the compare logic is a NO-OP. |

| 20<br>21                             | B14        | B13           |                                                                 |

| 22<br>23                             | B12        | B11           |                                                                 |

| 24<br>25<br>26                       | B10<br>B08 | в09<br>в07    |                                                                 |

| 27<br>28                             | воб        | B05           | **at the end of micro-step 35, ∞                                |

| 29<br>30                             | во4        | в03           | and & reset to 0.                                               |

| 31<br>32                             | в02        | B01           |                                                                 |

| 33<br>34<br>35                       | в00        | 0             |                                                                 |

| **                                   |            |               |                                                                 |

The PICU does not directly participate in the actual search. It sends controls to the elements directing the element to generate the A, B and C lines, to do the mapping, to compare the X, Y and Z lines and to reset the element activity if the compare so indicates. The PICU can end the search early. If during the execution of the search instruction, the element activity count goes to one, the PICU terminates execution of the instruction. This early end is possible because, if there is only one element left, it has the highest or lowest valued A register in the set of active elements. This logic is described in detail in section 4.2.

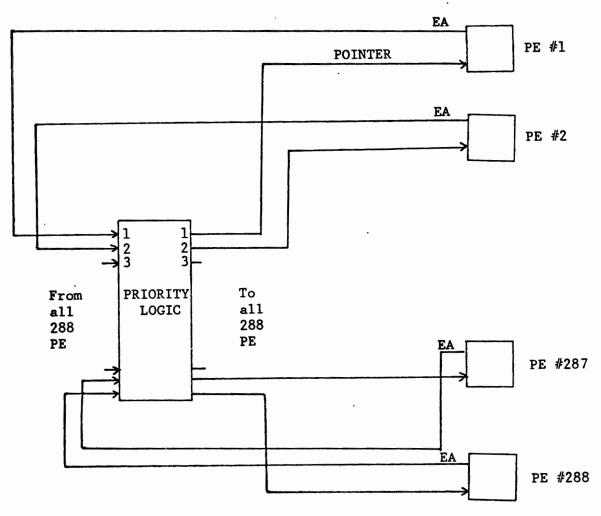

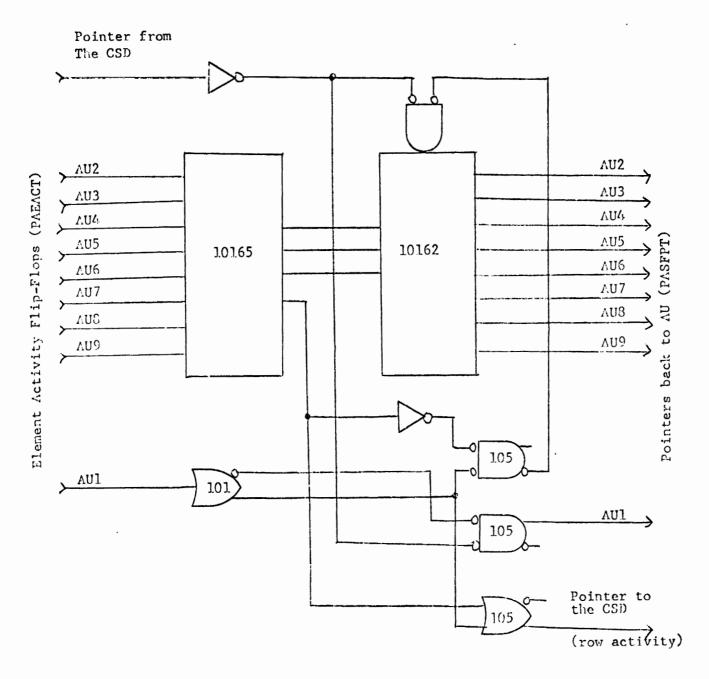

3.6.3 Select First

Following the execution of a SH, SL or other select instruction, many AU may still remain active. If we wish to extract a data item via the ODB, we require only one active AU. The Select First (SF) instruction, will cause all but one AU to reset its EA.

The one AU selected to remain active will be the "first" one found.

"First" is defined as the AU within the lowest numbered PE. As shown in

Figure 3.10, each AU supplies its EA to the priority logic. This logic

then determines the lowest numbered AU and returns a pointer to this AU.

The priority logic is always active. During the execution of a SF instruction, the AU is commanded to load the pointer ("one" or "zero") into its

EA flip-flop thus selecting one AU.

The priority logic is contained within each Bay and the CC.

Processing Elements are Numbered on the Basis of Physical Location

Figure 3.10 Select First Block Diagram

## 4.0 Detail Design of the AU

In this section I will describe in detail the implementation of the algorithms explained in Section 3. After a description of the physical hardware, I will show how the PICU controls the AU. Finally, the special hardware which enables the AU to perform as an efficient parallel associative processor is described.

#### 4.1 Hardware

The selection of the physical and electrical parameters of PEPE played an important role in its success.

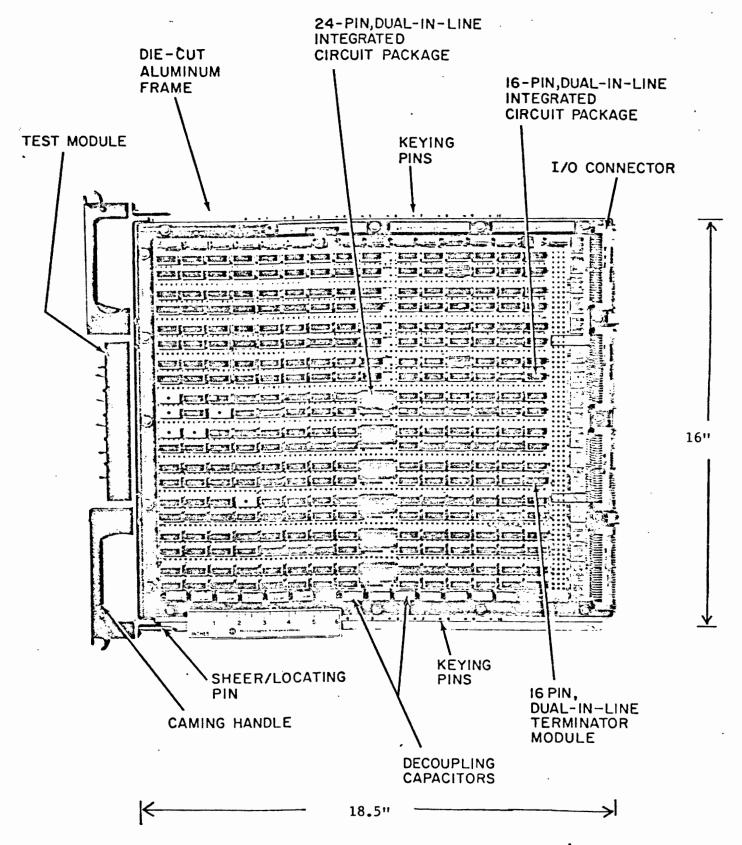

## 4.1.1 Circuits - ECL

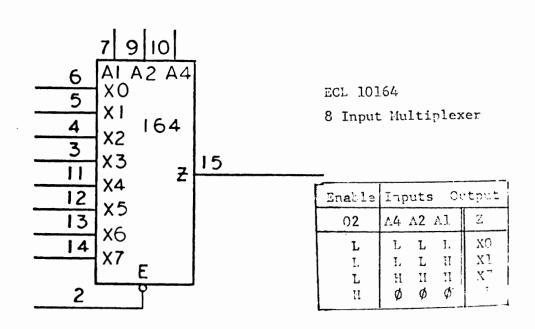

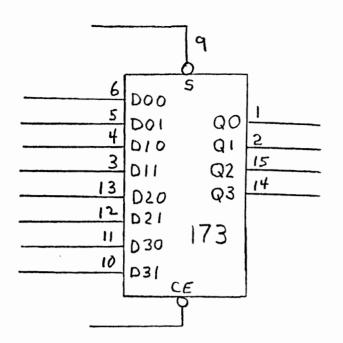

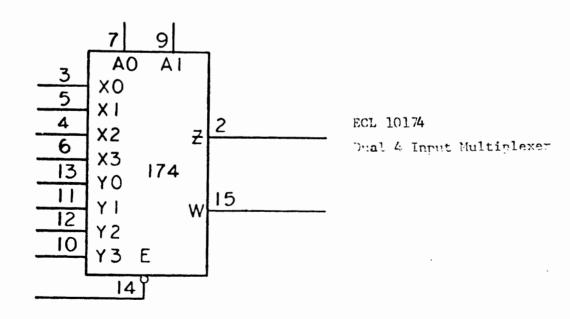

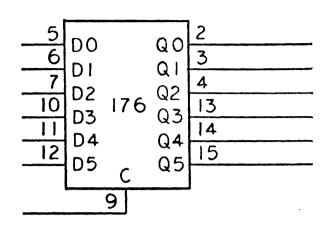

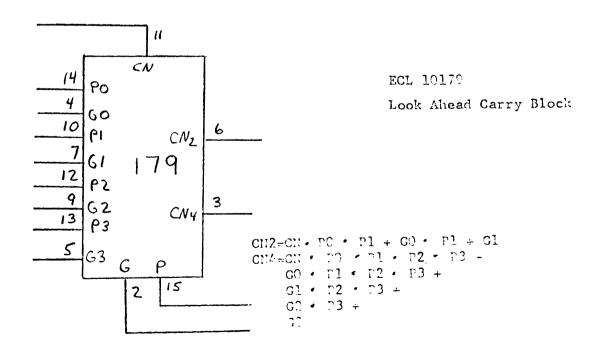

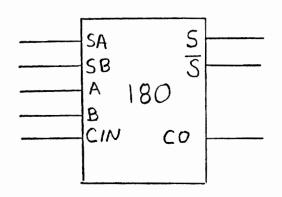

The AU is designed using readily available 10K series Emitter Coupled Logic (ECL). Appendix D lists the package types used along with the logic symbols and truth tables for the more complex Medium Scale Integration (MSI) chips.

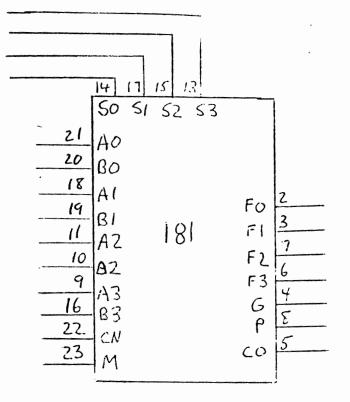

The use of 10K series logic with its two nanosecond typical delay times permits the AU to execute at a speed of 100 ns per micro-step. With the exception of the 10181 each of these chips is mounted in a 16 pin Dual-In-Line Package (DIP). The 10181 is a 24 pin DIP.

In the remainder of this section, the five digit 10K gate type will generally be abbreviated to the last three digits.

#### 4.1.2 Boards

The AU was fabricated on two large printed circuit boards. The boards, which were specially designed for PEPE, contain eight printed circuit layers. Four of these layers carry ECL signals. Each printed line is controlled during manufacture to maintain a 55 ohm impedence. Two of the remaining layers distribute voltages to the DIPs. Voltages used are a

VCC of +2 and a VEE of -3.2. Finally, the last two layers are ground, used both for DC reference and as a ground plane for the signal lines.

In addition to printed circuit, the board can be wirewrapped with open wire and miniature coaxial cable. All of the signal carrying media are controlled impedance (55 ohm) lines. Since these lines are similar to high frequency transmission cables, they are properly terminated with a 55 ohm resistive load to minimize reflections.

Shown in figure 4.1, the board can hold up to 300 16-pin DIPS.

Since the ALU (181) is a 24-pin DIP, special provision was made to permit up to 10 24-pin sockets in the center of the board. Each 24 pin socket replaces two 16 pin sockets. In the final AU design, board AU1 contains 201 16-pin ECL DIPS, 3 24-pin 181 DIPS and 73 16 pin 55 - terminator modules. Board AU2 contains 219 16-pin ECL DIPS, 6 24-pin 181 DIPS and 67 16 pin terminator modules.

Interconnection into the backplane for signals, power and ground is through four 100 pin connectors. 256 of the 400 pins are available for signals.

# 4.1.3 Backplane

Each AU board plugs into a 55 slot backplane/card rack assembly.

The backplane can accommodate nine processing elements. It is a three layer laminated assembly used not only for physical support but also for power distribution. Power enters the board from the backplane via the two center 100 pin connectors which are mounted on the backplane.

Figure 4.2 shows a rear view of the Element Bay. The Bay houses four backplane/card rack assemblies and power supply for each row. The power bussing scheme is designed as a low inductance distribution network to provide power to the row with less than a 50 milli-volt drop along the five foot backplane.

Figure 4.1 PEPE Printed Circuit Board

Figure 4.2 Element Bay Backplane

All signal interconnections between boards of the PE are via the three bottom connectors of the boards. Miniature coaxial cable is used as the media. The top connector (P1) uses a specially designed signal distribution scheme using belted cable. The belted cable carries control signals from the BSD to the PE in the row. The regular pattern of cables seen in Figure 4.2 serve to outline each PE. The signalling method used on these cables is differential balanced pair. This provides immunity to both resistive voltage losses and common mode injected noise. The Output Data Bus is also carried on these belted cables.

The control signals reach these belts after originating in the PICU and travelling through the Signal Distribution System. Upon reaching the AU, they cause registers, selectors and functional units to execute the instruction decoded in the PICU. These control lines will be described in the remainder of this section. Appendix E will serve as a quick reference for signal names used in this section.

## 4.2 Parallel Instruction Control Unit

The control lines for the AU are generated by the Parallel Instruction

Control Unit (PICU) in the Control Console. The PICU contains a Micro

Program Memory (MPM) that stores the control bits for each micro-step. The

PICU also contains control logic for correct sequencing of each instruction.

4.2.1 Purpose/MPM

The ACU-PICU is part of the Arithmetic Control Unit and is supplied parallel instructions and data from the ACU-SCL. The purpose of the PICU is to cause parallel element AU's to properly perform parallel instructions by transmitting, through the Signal Distribution System, global control and data. The PICU must also interface with the Element Memory Control (EMC) to assure proper operation in the event of Element Memory access conflicts with the two other processors in each PE.

#### 4.2.2 Operation

Figure 4.3 shows a block diagram of the ACU-PICU. The following paragraphs describe the operation of each block.

#### 4.2.2.1 PICU Interfaces

## 4.2.2.1.1 ACU-SCL/PIQ

The PICU receives instructions and data from the SCL/PIQ. These data are presented to the PICU on 47 lines:

| SAIINP(31-0)          | 32 bit operand       |

|-----------------------|----------------------|

| <b>SAIINP</b> (39-32) | 8 bit opcode         |

| SAIINO(40)            | R (EM reference) bit |

| <b>SAIINP(45-41)</b>  | not used in ACU-PICU |

| SAIINP(46)            | EM look-ahead bit    |

The PICU signals with SAIEMT when it has completed execution of its parallel instruction. The SCL/PIQ signals with SAIREQ to the PICU when a new parallel instruction is available. The PICU acknowledges receipt of the instruction with SAIACK.

Figure 4.3 ACU-PICU Block Diagram

## 4.2.2.1.2 Element Memory Control (EMC)

When the PICU requires EM access during the course of a parallel instruction execution, it signals the EMC by:

- 1. Placing the EM address on address bus PADAIN

- 2. Signaling read or write with line PADMDE

- 3. Requesting access by raising line PADREQ

When the EMC has selected the ACU-PICU for service, it responds with PADSEL. The PICU then utilizes this signal to gate the EM data bus to or from the AU.

## 4.2.2.1.3 Signal Distribution System (SDS)

The PICU receives one signal from the SDS. Named, SAMANY, it is derived from the AU count logic (see section 3.6.1) and indicates that more than one AU in the ensemble are active.

Since the AU contain little execution control logic (they are composed of registers and selectors), all switching control and data strobe signals are generated by the PICU and transmitted to the ensemble of AU through the SDS.

# 4.2.2.1.4 Output Data Control (ODC)

The ODC transmits PAOSEL to the ACU-PICU during the execution of an OTA instruction. The PICU then causes the active AU to place the contents of its A Register on the Output Data Bus.

# 4.2.2.1.5 Intercommunication Logic (ICL)

A special purpose interface exists to the ICL. It does not affect operation of the AU and will not be discussed here.

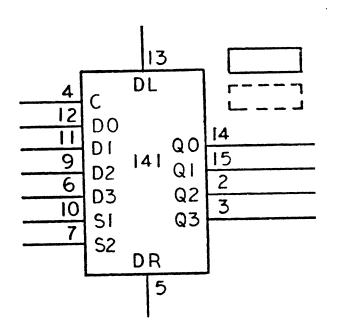

## 4.2.2.2 Micro-Program Memory

The MPM consists of 1024 words each 80 bits wide. The memory is addressed with 9 bits, the 8 bit opcode and the R bit. The next address field contains the address of the next micro-step. This field allows jumps within the MPM. The global control line field bits are used to define steering gates and register strobes in the ensemble AU which allow data to pass from one register to another. These lines are discussed in detail in Section 4.3.

The local PICU control line field is used to control operations within the PICU. Some of the local control bits are listed:

- PADREQ Request for EM cycle to EMC.

- PADMDE R/W indicator to EMC.

- PAMEOI End of instruction bit. Causes the control to switch

the next parallel instruction opcode from the SCL/PIQ

into the memory address register. Otherwise the MPM

next address field is used.

- PAMGDT A two bit field used to select one of the following as

input to bits 31-0 of the PAMORL Output Register:

- 2. Mask Generation Logic

- 3. MPM Global Control Bits (31-0)

- PAMEXT Set to "1" for each micro-step of a Select Highest/

Lowest instruction. It is used to affect an early

exit from these instruction when only one AU remains

active. Section 3.6.2 describes its use in more detail.

The MPM is constructed of 1024 X 1 bit RAM and is loaded from the Test and Maintenance Computer.

#### 4.2.2.3 Memory Address Register (PAMMAR)

PAMMAR supplies address lines to the MPM. It is loaded from the MPM next address field or from SCL/PIQ lines 40-32.

# 4.2.2.4 Operand Buffer Register (PAMOBR)

Thirty-two bits from the SCL/PIQ are gated into the PAMOBR when the parallel instruction is transferred into the PICU. The data represents the parallel instruction operand. It may be required during any, or none, of the micro-steps of the instruction. The Output Register selector will determine, based on PAMGDT, if and when the PAMOBR will be selected onto the PAMORL lines.

When a request is made to EMC, the lower ten bits are sent as the EM address.

Bits 15-11 are transferred to the Mask Generate Logic during execution of the instructions RBIT, SBIT, PSEL and SELB.

# 4.2.2.5 Output Register (PAMORL)

The PAMORL holds the current micro-step data and control being transmitted to the ensemble AU. Input to the register is controlled by PAMGDT (paragraph 4.2.2.2).

## 4.2.2.6 Mask Generate Logic

In order to make efficient use of EM, instructions are provided which operate on a single bit of memory at a time. The instructions are SBIT, RBIT, PSEL and SELB. They are implemented in the AU by performing logical operations over the entire 32 bit data word. To protect the 31 bits that are not involved in the instruction, the PICU generates a mask.

The mask for RBIT will contain "ones" in every bit position except for the bit indicated by PAMOBR(15-11). The mask for SBIT, PSEL and SELB will be all "zeros" with a single "one".

# 4.2.2.7 Timing and Control

This block performs all of the control functions of the PICU and handles all of the interfaces.

It generates PAGEN, the general clock-strobe, to the AU, causing the AU to execute the current micro-step.

## 4.2.2.8 The R bit

The R or routing bit is generated by the SCL when decoding the instruction. If the programmer specified a global operand, the R bit is "zero" and the PAMOBR is passed to the AU. If an EM operand was specified, the R bit is a "one". The PICU requests an EM cycle and causes the AU to use its local EM data bus as the source of the operand. The PICU implements this by using the R bit as an address bit in accessing MPM. The AU is then caused to execute a different micro-sequence based on the operand source.

# 4.3 Detail Block Diagram

Figure 4.4 shows a detail block diagram of the AU. Depicted are all of the registers, flip-flops, selectors, functional units and data paths.

Each of these receives a control line originating in the PICU MPM. That control line or lines causes actions which enable the AU to perform instructions. Table 4.1 relates the bit numbers of the PICU Output Register (PAMORL) to the AU control line names.

## 4.3.1 Registers/Flip-Flops

Table 4.2 lists the control lines for the registers in the AU and

Table 4.3 lists the lines for the flip-flops. A "one" on the control line

causes the storage element to load the contents of its input lines under

the following conditions:

- Since the instruction stream to the AU may not be continuous,

signal PAGEN is sent to all AU by the PICU. If PAGEN is

"zero" no storage elements are permitted to change state in the AU.

- If the AU is inactive (PAEACT is reset), no user visible registers are permitted to change state with minor exceptions.

The instructions which execute in an inactive AU are only those which can activate the AU.

- If the entire PE is faulted (PAFALT is set), the AU will not respond to any instruction except "clear fault" (CF). No user visible storage element is permitted to change state.

- 4.3.1.1 A Register Mantissa PAAREG(23-0)

STROBE=PAEACT PAFALT PAMORL19

Figure 4.4a PEPE AU Detailed Block Diagram

Figure 4.4b PEPE AU Detail Block Diagram

| PAMORL<br>BIT NO. | SIGNAL NAME FOR PAMORL 48=0      | DEFINITION                                                                                                  |

|-------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------|

| 00<br>01<br>02    | #PAADMOO<br>#PAADMO1<br>#PADDMO2 | Adder Control (ALU)                                                                                         |

| 03<br>04<br>05    | #PAADMO3<br>#PAAMAOO<br>#PAAMAO1 | Adder Control Adder mantissa, A input select                                                                |

| · 06<br>07<br>08  | #PAAMAO2<br>#PAAMBOO<br>#PAAMBO1 | Adder mantissa, A input select<br>Adder mantissa, B input select<br>Adder mantissa, B input select          |

| 09<br>10<br>11    | #PAAEBOO<br>#PAAEBO1<br>#PAAEAOO | Adder exponent, B input select<br>Adder exponent, B input select<br>Adder exponent, A input select          |

| 12<br>13<br>14    | #PAAEAO1<br>#PAAEAO2<br>#PAAMSOO | Adder exponent, A input select A register, mantissa input select                                            |

| 15<br>16<br>17    | #PAAMSO1<br>#PAAESOO<br>#PAAESO1 | A register, mantissa input select A register, exponent input select                                         |

| 18<br>19<br>20    | #PAAESO2<br>#PAAMM<br>#PAAEM     | A register, exponent input select<br>Clock enable, A mantissa<br>Clock enable, A exponent                   |

| 21<br>22<br>23    | #PAQMSOO<br>#PAQMSO1<br>#PAQESOO | Q register, mantissa input select<br>Q register, mantissa input select<br>Q register, exponent input select |

| 24<br>25          | #PAINSOO<br>#PAINSO1             | Local control decode                                                                                        |

| 26<br>27<br>28    | #PAINSO2<br>#PAINSO3<br>#PAINSO4 | Local control decode                                                                                        |

| 29<br>30<br>31    | #PAALO<br>#PAALNOO<br>#PAALNO1   | Alignment network control Alignment network input select Alignment network input select                     |

|                   | FOR<br>PAMORL 48=1               |                                                                                                             |

| 31-00             | PAXDIN                           | Global Data From PICU                                                                                       |

TABLE 4.1, CONTROL SIGNALS, AU

| PAMORL<br>BIT NO | SIGNAL NAME<br>FOR 49=1 | DEFINITION                                                                                        |

|------------------|-------------------------|---------------------------------------------------------------------------------------------------|

| 32               | #PASTK                  | Clock enable, stack register                                                                      |

| 33               | #PAEAZOO                | Element activity control decoder input                                                            |

| 34               | #PAEAZO1                | Element activity control decoder input                                                            |

| 35               | #PAEAZO2                | Element activity control decoder input                                                            |

| 36               | #PAEAZO3                | Element activity control decoder input                                                            |

| 37               | #PAEAZO4                | Element activity control decoder input                                                            |

| 38               | #PATGS00                | Tag register, input select                                                                        |

| 39               | #PATGSO1                | Tag register, input select                                                                        |

| 40               | #PAEAC                  | Clock enable, element activity flip-flop                                                          |

| 41               | #PADPC                  | Clock enable, double precision carry                                                              |

| 42               | #PATAG                  | Clock enable, tag register                                                                        |

| 43               | #PASTKOO                | Stack register, input select                                                                      |

| 44               | #PASTKO1                | Stack register, input select                                                                      |

|                  | SIGNAL NAME<br>FOR 49=0 |                                                                                                   |

| 32               | #PANOR                  | Alignment network control                                                                         |

| 33               | #PAFIX                  | <pre>Special control inhibit A reg mantissa   Clock during microstep 5 of FIX   instruction</pre> |

| 34               | #PATOV                  | Clock enable, temporary overflow hold FF                                                          |

| 35               | #PACO-23                | Clock enable, carry out 23 hold FF                                                                |

| 36               | #PAQMM                  | Clock enable, Q mantissa                                                                          |

| 37               | #PAQEM                  | Clock enable, Q exponent                                                                          |

| 38               | #PABMSOO                | B register, mantissa input select                                                                 |

| 39               | #PABMSO1                | B register, mantissa input select                                                                 |

| 40               | #PABESOO                | B register, exponent input select                                                                 |

| 41               | #PABESO1                | B register, exponent input select                                                                 |

| 42               | #PABMMO1                | Clock enable, B mantissa bits 7-0                                                                 |

| 43               | #PABMMO2                | Clock enable, B mantissa bits 23-8                                                                |

| 44               | #PABEM                  | Clock enable, B exponent                                                                          |

|                  |                         |                                                                                                   |

| 45               | #PAASCS00               | Shift control register, input select                                                              |

| 46               | #PASCS01                | Shift control register, input select                                                              |

| 47               | #PAOV                   | Clock enable, PAOVFF flip-flop                                                                    |

| 48               | #PADTC                  | Control signal, data time shared with control                                                     |

| 49               | #PACTC                  | Control signal, select control group                                                              |

| 50               | #PASCR                  | Clock enable, shift count register                                                                |

| 51               | #PARVM                  | PAXDIN input select                                                                               |

| - 1              | The meening of DAM      | OPI (21 0) lines is dependent on DAMODI 49                                                        |

- a) The meaning of PAMORL (31-0) lines is dependent on PAMORL 48.

- b) The meaning of PAMORL (44-32) lines is dependent on PAMORL 49.

| REGISTER (Bit #)       | CONTROL LINE |

|------------------------|--------------|

| A_(23-0)               | PAMORL19     |

| A <sub>x</sub> (31-24) | PAMORL20     |

| B_(7-0)                | PAMORL42     |

| B <sub>m</sub> (23-8)  | PAMORL43     |

| B <sub>x</sub> (31-24) | PAMORL44     |

| B (Extension bit)      | None         |

| Q_(23-0)               | PAMORL36     |

| Q (31-24)              | PAMORL37     |

| Q (Extension bit)      | None         |

| Shift Count Register   | PAMORL50     |

| Tag Register           | PAMORL42     |

| Activity Stack         | PAMORL32     |

|                        |              |

Table 4.2 Register Control

| CONTROL FLIP-FLOP | CONTROL LINE  |

|-------------------|---------------|

| PAEACT            | PAMORL40      |

| PAFALT            | Local Control |

| PAZROA            | Lbcal Control |

| PAZROB            | Local Control |

| PASIGN            | Local Control |

| PADPC             | PAMORL41      |

| PATOVF            | PAMORL34      |

| PAOVFF            | PAMORL47      |

| PACO23FF          | PAMORL35      |

Table 4.3 Flip-Flop Control

- 4.3.1.2 A Register Exponent PAAREG(31-24)

STROBE=PAMORL20 PAEACT PAFALT

- 4.3.1.3 B Register Mantissa 1 PABREG(7-0)

STROBE = PAMORL42 PAFALT

- 4.3.1.4 B Register Mantissa 2 PABREG(23-8)

STROBE = PAMORL43 PAFALT

- 4.3.1.5 B Register Exponent PABREG(31-24)

STROBE = PAMORL44 PAFALT

- **4.3.1.6** Q Register Mantissa PAQREG(23-0)

STROBE = PAMORL36 PAFALT PAEACT

- 4.3.1.7 Q Register Exponent PAQREG(31-24)

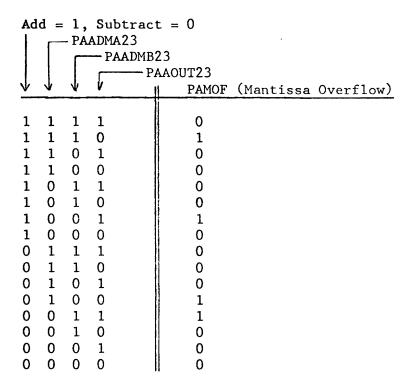

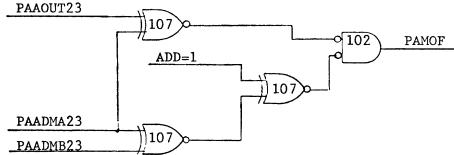

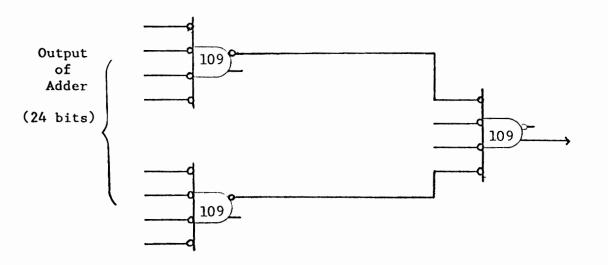

STROBE = PAMORL37 PAFALT PAEACT